MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。

MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。

MOS电路的应用

MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。CMOS数字集成电路电路主要分为4000(4500系列)系列、54HC/74HC系列、54HCT/74HCT系列等,实际上这三大系列之间的引脚功能、排列顺序是相同的,只是某些参数不同而已。

例如,74HC4017与CD4017为功能相同、引脚排列相同的电路,前者的工作速度高,工作电源电压低。4000系列中目前最常用的是B系列,它采用了硅栅工艺和双缓冲输出结构。

Bi-CMOS是双极型CMOS(Bipolar-CMOS)电路的简称,这种门电路的特点是逻辑部分采用CMOS结构,输出级采用双极型三极管,因此兼有CMOS电路的低功耗和双极型电路输出阻抗低的优点。

低压应用

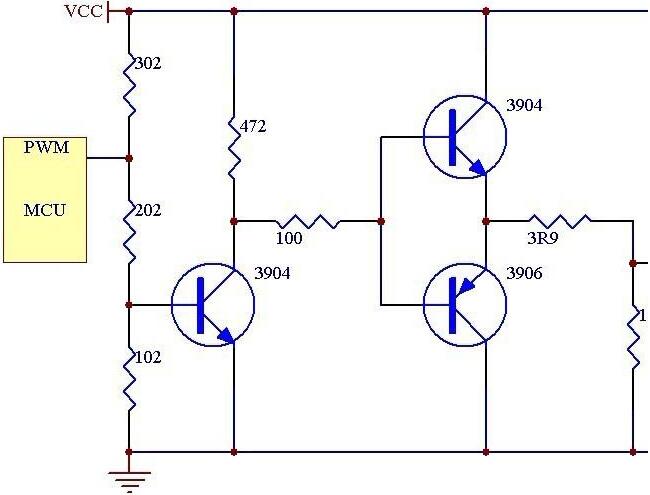

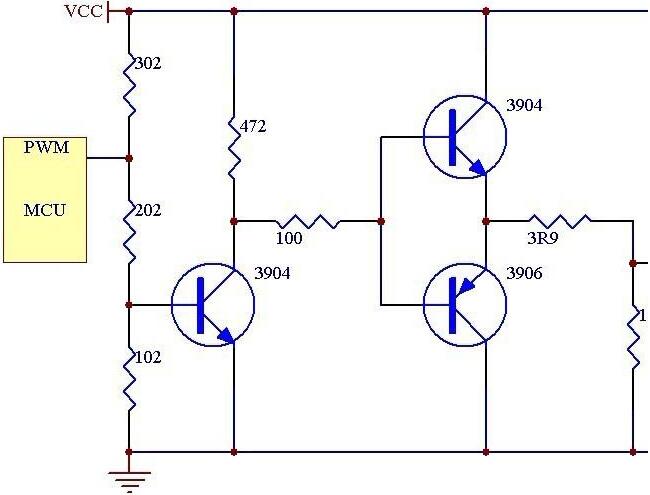

当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有0.7V左右的压降,导致实际最终加在gate上的电压只有4.3V。这时候,我们选用标称gate电压4.5V的MOS管就存在一定的风险。同样的问题也发生在使用3V或者其他低压电源的场合。

宽电压应用

输入电压并不是一个固定值,它会随着时间或者其他因素而变动。这个变动导致PWM电路提供给MOS管的驱动电压是不稳定的。为了让MOS管在高gate电压下安全,很多MOS管内置了稳压管强行限制gate电压的幅值。在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较大的静态功耗。同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗。

双电压应用

在一些控制电路中,逻辑部分使用典型的5V或者3.3V数字电压,而功率部分使用12V甚至更高的电压。两个电压采用共地方式连接。这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的MOS管,同时高压侧的MOS管也同样会面对1和2中提到的问题。在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的MOS驱动IC,似乎也没有包含gate电压限制的结构。

MOS电路图

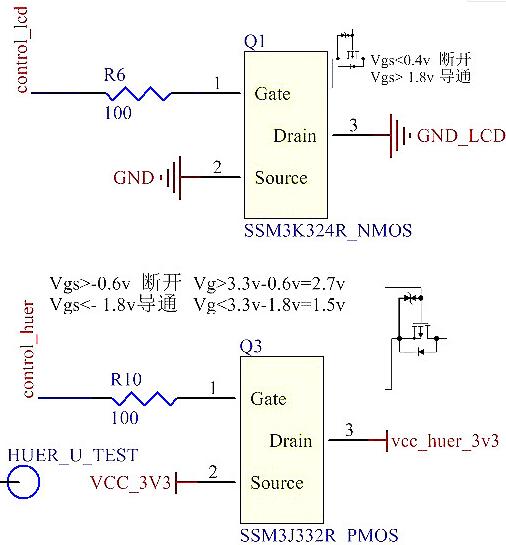

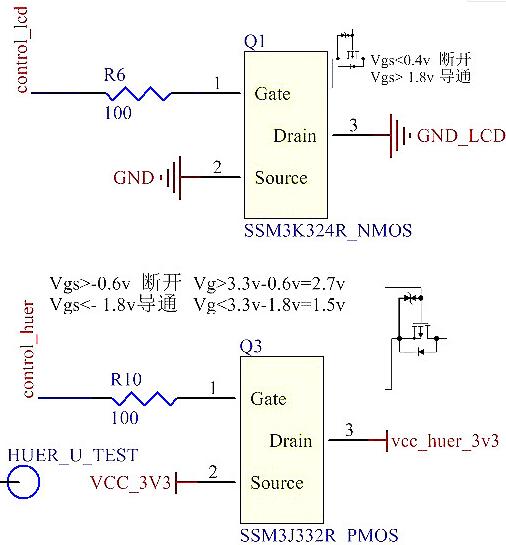

P沟道MOS管开关电路

下图是两种P沟道MOS管开关电路应用:其中第一种NMOS管为高电平导通,低电平截断,Drain端接后面电路的接地端;第二种为P沟道MOS管开关电路,为高电平断开,低电平导通,Drain端接后面电路的VCC端。

P沟道MOS管开关电路工作原理

金属氧化物半导体场效应(MOS)晶体管可分为N沟道与P沟道两大类, P沟道硅MOS场效应晶体管在N型硅衬底上有两个P+区,分别叫做源极和漏极,两极之间不通导,柵极上加有足够的正电压(源极接地)时,柵极下的N型硅表面呈现P型反型层,成为衔接源极和漏极的沟道。改动栅压可以改动沟道中的电子密度,从而改动沟道的电阻。这种MOS场效应晶体管称为P沟道增强型场效应晶体管。

假设N型硅衬底表面不加栅压就已存在P型反型层沟道,加上恰当的偏压,可使沟道的电阻增大或减小。这样的MOS场效应晶体管称为P沟道耗尽型场效应晶体管。统称为PMOS晶体管。

P沟道MOS晶体管的空穴迁移率低,因而在MOS晶体管的几何尺寸和工作电压绝对值相等的情况下,PMOS晶体管的跨导小于N沟道MOS晶体管。此外,P沟道MOS晶体管阈值电压的绝对值普通偏高,恳求有较高的工作电压。它的供电电源的电压大小和极性,与双极型晶体管——晶体管逻辑电路不兼容。PMOS因逻辑摆幅大,充电放电过程长,加之器件跨导小,所以工作速度更低,在P沟道MOS管开关电路(见N沟道金属—氧化物—半导体集成电路)呈现之后,多数已为NMOS电路所取代。

只是,因PMOS电路工艺简单,价钱低价,有些中范围和小范围数字控制电路仍采用PMOS电路技术。PMOS的特性,Vgs小于一定的值就会导通,适宜用于源极接VCC时的情况(高端驱动)。但是,固然PMOS可以很便当地用作高端驱动,但由于导通电阻大,价钱贵,交流种类少等缘由,在高端驱动中,通常还是运用NMOS。

正常工作时,P沟道增强型MOS管的衬底必需与源极相连,而漏心极的电压Vds应为负值,以保证两个P区与衬底之间的PN结均为反偏,同时为了在衬底顶表面左近构成导电沟道,栅极对源极的电压Vgs也应为负。

1.Vds≠O的情况导电沟道构成以后,DS间加负向电压时,那么在源极与漏极之间将有漏极电流Id流通,而且Id随Vds而增加.Id沿沟道产生的压降使沟道上各点与栅极间的电压不再相等,该电压削弱了栅极中负电荷电场的作用,使沟道从漏极到源极逐渐变窄.当Vds增大到使Vgd=Vgs(TH),沟道在漏极左近呈现预夹断.2.导电沟道的构成(Vds=0)当Vds=0时,在栅源之间加负电压Vgs,由于绝缘层的存在,故没有电流,但是金属栅极被补充电而聚集负电荷,N型半导体中的多子电子被负电荷排斥向体内运动,表面留下带正电的离子,构成耗尽层,随着G、S间负电压的增加,耗尽层加宽,当Vgs增大到一定值时,衬底中的空穴(少子)被栅极中的负电荷吸收到表面,在耗尽层和绝缘层之间构成一个P型薄层,称反型层,这个反型层就构成漏源之间的导电沟道,这时的Vgs称为开启电压Vgs(th),Vgs到Vgs(th)后再增加,衬底表面感应的空穴越多,反型层加宽,而耗尽层的宽度却不再变化,这样我们可以用Vgs的大小控制导电沟道的宽度。

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍