boost升压电路又叫step-up converter,是一种常见的开关直流升压电路,它可以使输出电压比输入电压高。

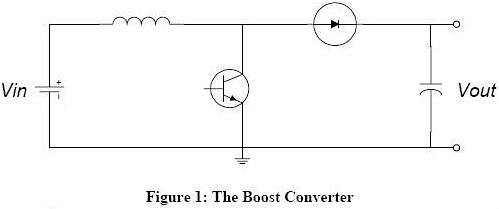

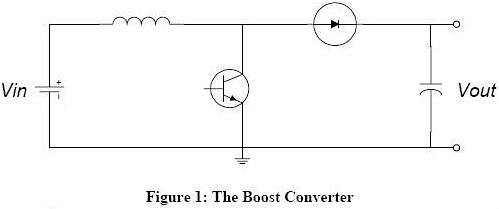

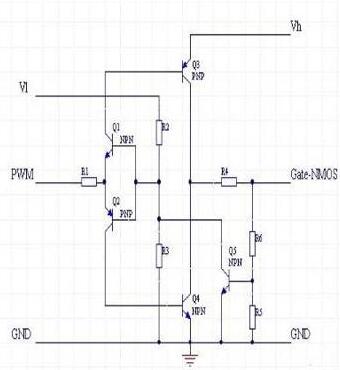

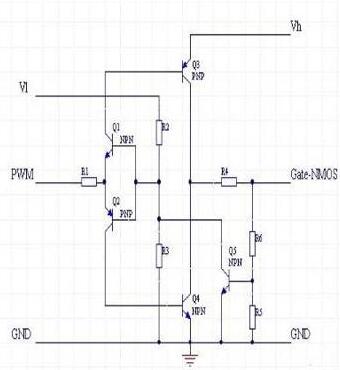

升压电路电路图

假定那个开关(三极管或者mos管)已经断开了很长时间,所有的元件都处于理想状态,电容电压等于输入电压。分析升压斩波电路工作原理时,首先假设电路中电感L值很大,电容C值也很大。当可控开关V处于通态时,电源E向电感L充电,充电电流基本恒定为I1,同时电容C上的电压向负载供电。因为C值很大,基本能保持输出电压uo为恒值,记为Uo。设V处于通态的时间为ton,当V处于断态时E和L共同向电容C充电并向负载提供能量。设V处于关断的时间为toff,则在此期间电感L释放的能量为(Uo-E)I1toff。当电路工作于稳态时,一个周期T中电感L积蓄的能量与释放的能量相等。

下面要分充电和放电两个部分来说明这个电路:

mos管升压电路介绍

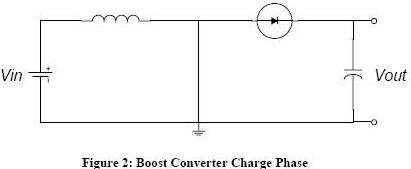

在充电过程中,开关闭合(三极管导通),等效电路如图二,开关(三极管)处用导线代替。这时,输入电压流过电感。二极管防止电容对地放电。由于输入是直流电,所以电感上的电流以一定的比率线性增加,这个比率跟电感大小有关。随着电感电流增加,电感里储存了一些能量。

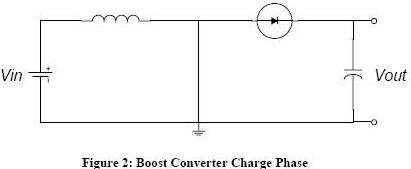

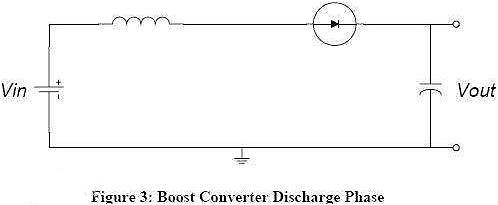

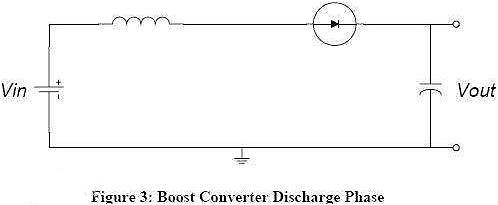

放电过程如图三,这是当开关断开(三极管截止)时的等效电路。当开关断开(三极管截止)时,由于电感的电流保持特性,流经电感的电流不会马上变为0,而是缓慢的由充电完毕时的值变为0。而原来的电路已断开,于是电感只能通过新电路放电,即电感开始给电容充电,电容两端电压升高,此时电压已经高于输入电压了。升压完毕。

说起来升压过程就是一个电感的能量传递过程。充电时,电感吸收能量,放电时电感放出能量。如果电容量足够大,那么在输出端就可以在放电过程中保持一个持续的电流。如果这个通断的过程不断重复。就可以在电容两端得到高于输入电压的电压。

mos管升压电路-MOS管驱动电路中自举升压结构

MOS管最明显的特征是开关特征好,因而被普遍使用在需求电子开关的电路中,常见的如开关电源和马达驱动,也有照明调光。即兴在的MOS驱动,有几个特殊的要求。

1.低压使用:当应用5V电源,这时辰如其应用传统的图腾柱构造,鉴于三极管的be有0.7V左右的压降,导致现实终极加以在gate上的电压除非4.3V。这时辰,咱们选用标称gate电压4.5V的MOS管就在必然的风险。同一的问题也产生在应用3V或者其他低压电源的场所。

2.宽电压使用:输入电压并不是一个恒定值,它会跟随时期或者其他要素而变动。这个变动导致PWM电路供给MOS管的驱动电压是不固定定的。为了让MOS管在高gate电压下安全,很多MOS管内置了固定压管强行限度局限gate电压的幅值。在这种情况下,当供的驱动电压超度过固定压管的电压,就会伸起较大的动态功耗。同步,如其简略的用电阻分压的规律下降gate电压,就会涌现输入电压比较高的时辰,MOS管任务良好,而输入电压下降的时辰gate电压不可,伸起导通不够到底,从而增添功耗。

3.双电压使用:在一些把持电路中,逻辑有些应用类型的5V或者3.3V数字电压,而功比值有些应用12V甚至更高的电压。两个电压选择共位置式连接。这就提出一个请求,需求应用一个电路,让低压侧能行有效的把持压服侧的MOS管,同步压服侧的MOS管也同在这三种情况下,图腾柱构造无法满意出口请求,而很多即兴成的MOS驱动IC,如同也没有包含gate电压限度局限的构造。

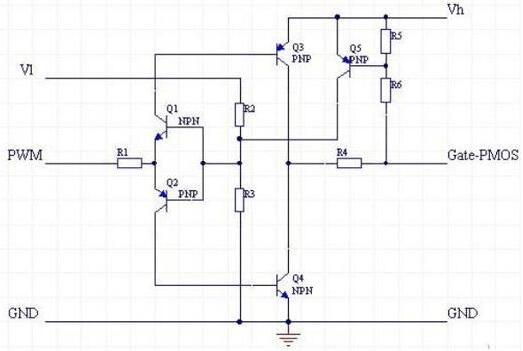

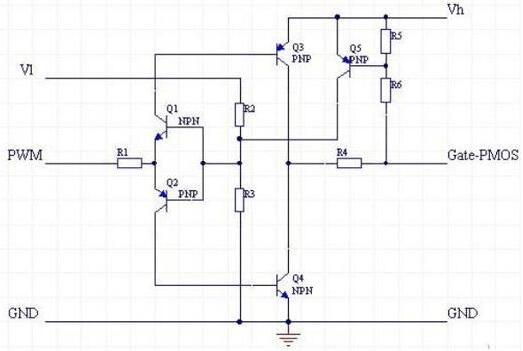

电路图如次:

用于NMOS的驱动电路

用于PMOS的驱动电路

只针对NMOS驱动电路做一个简略辨析:Vl和Vh区别是低端和高端的电源,两个电压可以是相通的,只是Vl不应当超度过Vh。Q1和Q2结合了一个反置的图腾柱,用来实即兴割裂,同步确保两只驱动管Q3和Q4不会同步导通。R2和R3供了PWM电压基准,经过转变这个基准,可以让电路任务在PWM记号波形比较峭拔的位置。Q3和Q4用来供驱动电流动,鉴于导通的时辰,Q3和Q4对立Vh和GND最低都除非一个Vce的压降,这个压降通常除非0.3V左右,大大低于0.7V的Vce。R5和R6是反馈电阻,用于对gate电压举行采样,采样后的电压经过Q5对Q1和Q2的基极发出一个激烈的负反馈,从而把gate电压限度局限在一个有限的数值。这个数值可以经过R5和R6来调整。

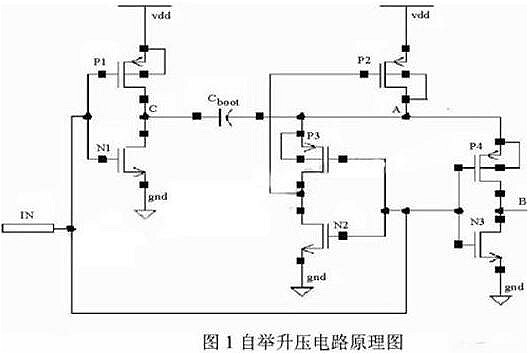

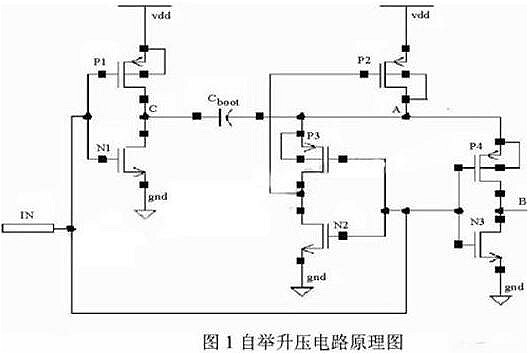

MOS管自举升压电路

mos管升压电路的规律图如图1所示。所谓的自举升压规律执意,在输入端IN输入一个方波记号,使用电容Cboot将A点电压抬升至高于VDD的电平,这么就可以在B端出口一个与信号输入反相,且高电平高于VDD的方波记号。具体任务规律如次:

当VIN为高电平时,NMOS管N1导通,PMOS管P1截止,C点电位为低电平。同步N2导通,P2的栅极电位为低电平,则P2导通。这就使得此刻A点电位约为VDD,电容Cboot两端电压UC≈VDD。鉴于N3导通,P4截止,因而B点的电位为低电平。这段时期称为预充电周期。

当VIN变为低电平时,NMOS管N1截止,PMOS管P1导通,C点电位为高电平,约为VDD。同步N2、N3截止,P3导通。这使得P2的栅极电位升天,P2截止。此刻A点电位等同C点电位加以上电容Cboot两端电压,约为2VDD。同时P4导通,故此B点出口高电平,且高于VDD。这段时期称为自举升压周期。

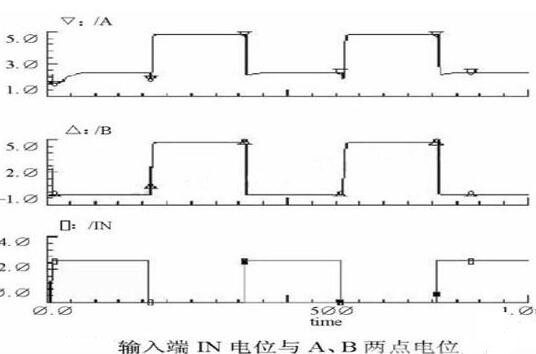

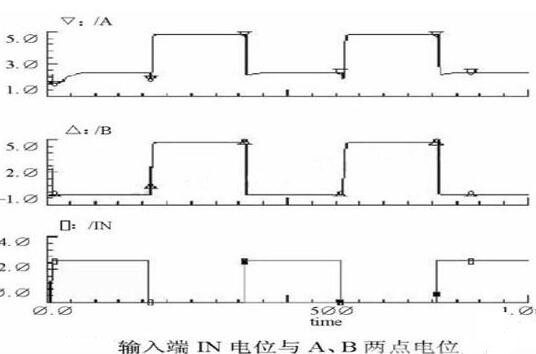

现实上,B点电位与负载电容和电容Cboot的大小关于,可以依据设计需求调理。具体相干将在绍介电路具体设计时仔细议论。在图2中给出了输入端IN电位与A、B两点电位相干的表图。

MOS管驱动电路构造

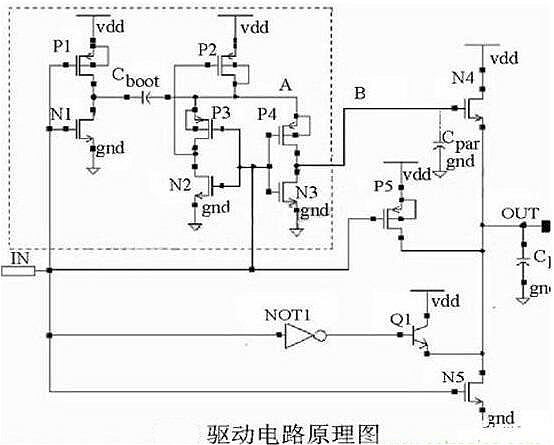

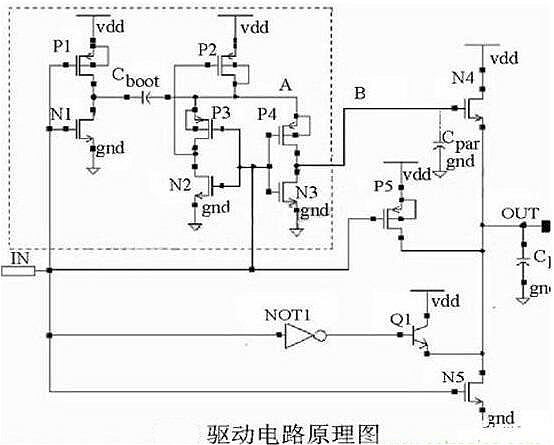

图3中给出了驱动电路的电路图。驱动电路选择Totem出口构造设计,上拉驱动管为NMOS管N4、晶体管Q1和PMOS管P5。下拉驱动管为NMOS管N5。图中CL为负载电容,Cpar为B点的寄生电容。虚线框内的电路为自举升压电路。

本驱动电路的设计思惟是,使用自举升压构造将上拉驱动管N4的栅极(B点)电位抬升,使得UB>VDD+VTH,则NMOS管N4任务在线性区,使得VDSN4大大减少,终极可以实即兴驱动出口高电平达成VDD。而在出口低电平时,下拉驱动管自己就任务在线性区,可以确保出口低电平位GND。故此无需增添自举电路也能达成设计请求。

思索到此驱动电路使用于升压型DC-DC替换器的开关管驱动,负载电容CL很大,一般能达成几十皮法,还需求进一步增添出口电流动能力,故此增添了晶体管Q1作为上拉驱动管。这么在输入端由高电平变为低电平时,Q1导通,由N4、Q1同步供电流动,OUT端电位神速上升,当OUT端电位上升到VDD-VBE时,Q1截止,N4持续供电流动对负载电容充电,直到OUT端电压达成VDD。

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍