一、阱构成技术

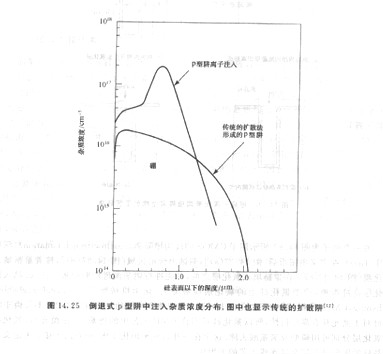

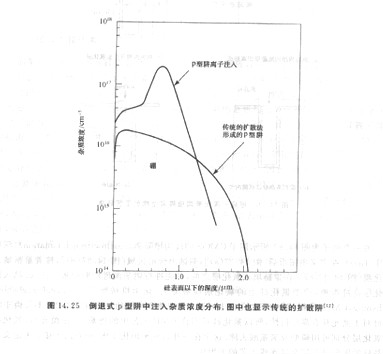

在CMOS中,阱可为单阱(single well)、双阱(twin well)或是倒退阱(retrograde well).双阱工艺有一些缺陷,如需高温工艺(超越1 050℃)及长扩散时间(超越8h)来到达所需2μm~31'm的深度,在这个工艺中,外表的掺杂浓度是最高的,掺杂浓度随着深度递加,为了降低工艺温度和时间,可应用高能量的离子注入将离子直接注入到想要的深度而不需经过外表扩散,如此一来,深度由离子注入的能量米决议,因而我们可用不同的注入能景来设计不同深度的阱.在这个工艺中,阱的掺杂散布峰值将位于硅衬底中的某个深度,因此被称为倒退阱,图14. 25显现在倒退阱与普通传统热扩散阱中掺杂散布的比拟,关于n型倒退阱与p型倒退阱而言,所需的能嚴分别为700keV及400keV.如前所提,高能离子注入的优点在于叮在低温及短时间的条件下构成阱,故可降低横向扩散及增加器件密度.倒退阱优于传统阱的中央有:①由于在底部的高掺杂浓度,倒退阱的阻值较传统阱低,所以能够将闩锁问题降至最低;②沟道阻断可与倒退阱的离子注入同时构成,减少工艺步骤与时间;③在底部较高的阱掺杂能够降低源极与漏极产生穿通(punch-rhrough,或译贯串、碰透)的几率.

二、先进隔离技术

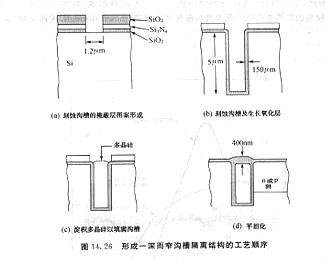

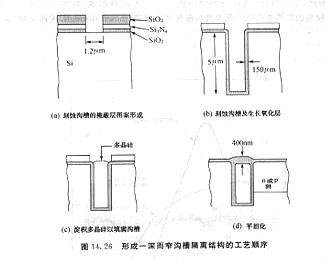

传统的隔离工艺(14,3,l节)有一些缺陷,使得其不合适用于深亚微米(小于o.25μ.m)工艺,硅的高温氧化与长氧化时间形成用于沟道阻断的注入离子(对n-MOSFET而言,通常为硼)侵入有源区域( active region)并招致VT偏移.因而,横向氧化会招致有源器件区域的面积减小,此外,在亚微米隔离的距离中,场氧化层的厚度明显小于生长在宽距离中的场氧化层,沟槽隔离技术能够防止这些问题,且已成为隔离的主流技术,图14. 26显现构成一深(大于3μm)而窄(小于2μm)的沟槽隔离技术的工艺次第,其包含四个步骤:开出图形、刻蚀硅衬底、填充介电资料(如二氧化硅或无掺杂的多晶硅)及平整化,深沟槽隔离可用于先进CMOS与双极型器件及沟槽式DRAM.由于隔离资料是应用CVD淀积,所以不需求长时间或高温工艺,且能够消弭横向氧化和硼侵入( boron encroachment)的问题.

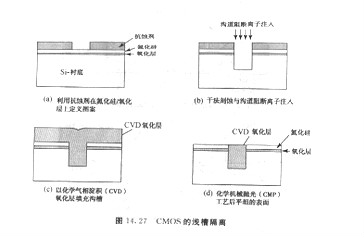

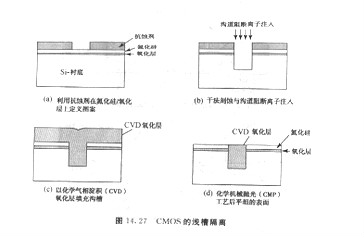

另一个例子为图14. 27所示用于CMOS的浅沟槽隔离(shallow trench isolation)(深度小于lμm).在定义出图形后(图14。27(a),刻蚀出沟槽区域[图14. 27(b》,接着重新填入氧化层[图14.27(C)].在重新填人氧化层之前,可先停止用于沟道阻断的离子注入,填入的氧化层高过沟槽,位于氮化硅上的氧化层应被除去,化学机械抛光( chemical-mechanicalpolishing,CMP)用来去除位于氮化硅上的氧化层以得到平整的外表[图14.27(d)].由于氮化硅关于抛光具有高抵御性,所以氮化硅可当作CMP工艺中的掩蔽层,在抛光后,氮化硅和氧化层分别可用磷酸及氢氟酸去除.这个在一开端的平整化步骤,将有助于接下来定义出多晶硅的图形及多层金属连线工艺的平整化.

三、栅极工程技术

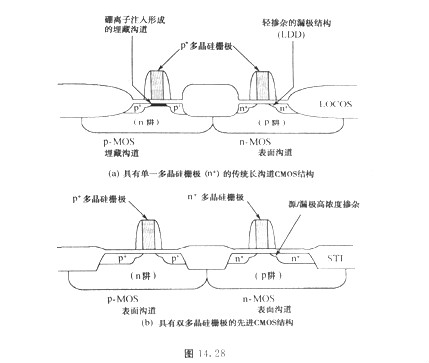

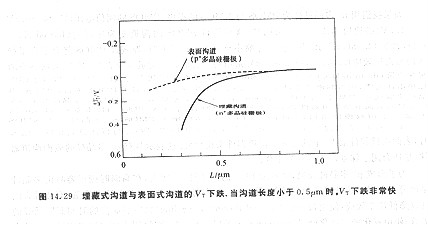

假如我们用n+多晶硅作为PMOS与NMOS的栅极,PMOS的阈值电压(vTP≈-o.5V~-1.OV)必需用硼离子注入来调整,这会使得PMOS的沟道变为埋藏式(buried chan-nel),如图14. 28(a)所示,当器件尺寸减少至o.25μm以下时,埋藏式PMOS将会遭遇很严重的短沟道效应(short channel effect).最值得留意的是短沟道效应有v,下跌、漏场感应的势垒降落(drain-induced barrier lowering,DIBL)及在关闭状态时大的漏电流,致使于即便栅极电压为零,也有漏电流经过源极与漏极.为处理这个问题,关于PMOS而言,可用p、多晶硅来取代n+多晶硅,由于功函数(work function)的差别(n+多晶硅与p、多晶硅有1.OeV的差别),外表p型沟道器件并不需求调整VT的硼离子注入,因而,当技术缩至o.25J'm以下,需求采用双栅极构造( dual-gate),即p+多晶硅用于PMOS,n+多晶硅用于NMOS[图14. 28(b》.外表沟道与埋藏沟道的Vl,比拟如图14. 29所示,能够留意到在深亚微米时,外表沟道器件的Vr下跌比埋藏沟道器件来得迟缓,这表示具有p+多晶硅的外表沟道器件,很合适用于深亚微米器件的工作,为了构成p’多晶硅栅极,通常用BFz、的离子注入,但是,在高温时硼很容易由多晶硅穿过薄氧化层抵达硅衬底而形成Vr偏移.此外,氟原子的存在会增加硼的穿透.有几种办法能够降低这个效应:运用快速退火(rapid thermal annealing)以减少高温的时间而降低硼的扩散,运用氮化的二氧化硅层(nitrided oxide)以抑止硼的穿透(由于硼能够很容易与氮分离而变得较不易挪动);制造多层的多晶硅,应用层与层间的界面去捕捉硼原子.

烜芯微专业制造二极管,三极管,MOS管,20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍