MOSFET非常重要的一项应用是开关电源,本文以德州仪器发布的《MOSFET和IGBT栅极驱动器电路的基本原理》为例,介绍MOSFET晶体管开通动作的4个阶段,包括开通及关断过程,栅极驱动损耗和开关损耗,以及影响开关性能的源极电感、漏极电感两个寄生元件的形成机理。

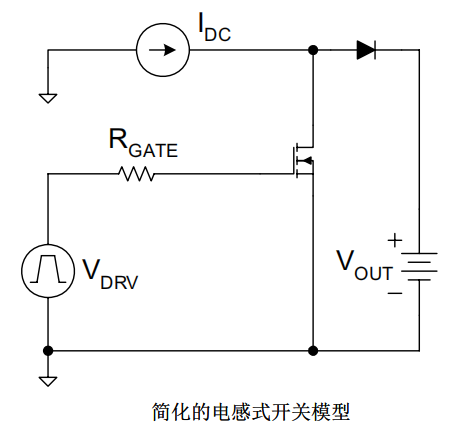

为了更好地理解开关过程,电路的寄生电感将被忽略。稍后将单独分析它对基本操作的相应影响。此外,以下描述涉及到箝位电感式开关,因为开关模式电源中所用的大多数MOSFET晶体管和高速栅极驱动电路都工作在该工作模式下。

简化的电感式开关模型图

在简化的MOSFET箝位电感式开关模型中,直流电流源代表电感器,在短暂的开关切换期间电流可以认为是常数。二极管在MOSFET关断时提供一条电流路径,并将器件的漏极箝位到由电池表示的输出电压。

开通过程

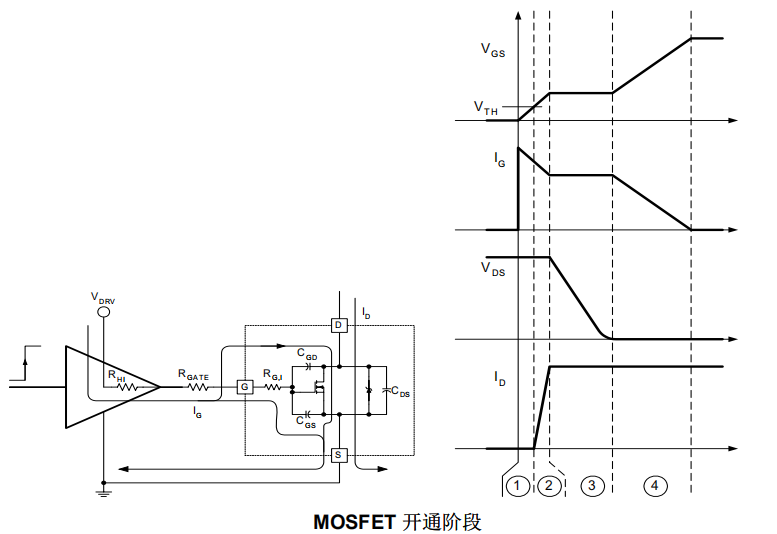

MOSFET晶体管的开通动作可分4个阶段。

第一步,器件的输入电容从0V充电至VTH。

MOSFET开通阶段图

在此期间,大部分栅极电流用于对CGS电容器充电,少量电流也会流经CGD电容器。随着栅极端子电压升高,CGD电容器的电压将略有下降。这个期间称为开通延时,因为器件的漏极电流和漏极电压保持不变。

栅极充电至阀值电平后,MOSFET就能载流了。在第二个阶段中,栅极电平从阀值VTH升高到米勒平坦电平VGS,Miller。当电流与栅极电压成正比时,这是器件的线性工作区。在栅极侧,就像在第一阶段中那样,电流流入CGS和CGD电容器中,并且VGS电压升高。在器件的输出端,漏极电流升高,同时漏源电压保持之前的电平(VDS,off)。在所有电流传输到MOSFET中并且二极管完全关断能够阻止其PN结上的反向电压之前,漏极电压必须保持输出电压电平。

进入开通过程第三阶段后,栅极已充电至足够电压(VGS, Miller),可以承载完整的负载电流且整流器二极管关断。此时,允许漏极电压下降。当器件上的漏极电压下降时,栅源极电压保持稳定。这就是栅极电压波形中的米勒平坦区域。驱动器提供的所有栅极电流都被转移,从而对CGD电容器充电,以便在漏源极端子上实现快速的电压变化。现在,器件的漏极电流受到外部电路(这是直流电流源)的限制,因此保持恒定。

开通过程的最后一步是通过施加更高的栅极驱动电压,充分增强MOSFET的导通通道。VGS的最终幅值决定了开通期间器件的最终导通电阻。所以,在第四阶段中,VGS从VGS,Miller上升至最终值VDRV。这通过对CGS和CGD电容器充电来实现,因此现在栅极电流在两个组件之间分流。当这些电容器充电时,漏极电流仍然保持恒定,而由于器件的导通电阻下降,漏源电压略有下降。

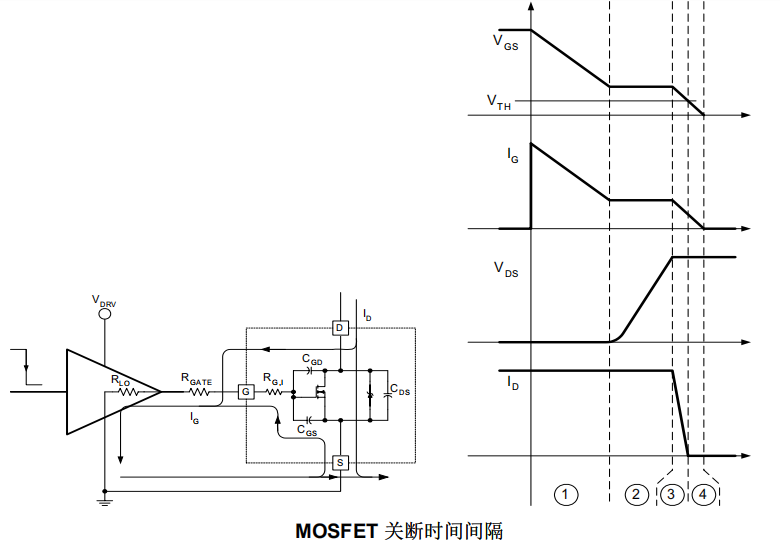

关断过程

MOSFET晶体管的关断过程说明基本上与上文所述的开通过程相反。开始时VGS等于VDRV,器件中的电流是由IDC表示的满负载电流。漏源电压由IDC和MOSFET的RDS(on)定义。

MOSFET关断时间间隔图

第一个阶段是关断延迟,需要将CISS电容从初始值放电至米勒平坦电平。在这段时间内,栅极电流由CISS电容器自己提供,并流经MOSFET的CGS和CGD电容器。随着过驱电压降低,器件的漏极电压略有上升,漏极的电流保持不变。

在第二阶段,MOSFET的漏源电压从ID×RDS(on)上升至最终的VDS,off电平,由整流器二极管箝位至输出电压。在此时间段内,与栅极电压波形中的米勒平坦区域对应,栅极电流完全是CGD电容器的充电电流,因为栅源极电压是恒定的。此电流由功率级旁路电容器提供,并从漏极电流中减去。总漏极电流仍然等于负载电流。

第三阶段的开始用二极管开通表示,因此为负载电流提供了一个替代路径。栅极电压继续从VGS,Miller下降至阀值VTH。

绝大部分栅极电流来自CGS电容器,因为CGD电容器实际上在前一个阶段中就已经充满电了。在此间隔结束时,MOSFET处于线性工作状态,栅源极电压下降导致漏极电流减小并接近于零。同时,由于正向偏置整流器二极管的作用,漏极电压在VDS,off时保持稳定。

关断过程的最后一步是对器件的输入电容完全放电。VGS进一步下降,直至达到0V。与第三关断阶段类似,栅极电流的更大一部分由CGS电容器提供。器件的漏极电流和漏极电压保持不变。

概括而言,在四个阶段中,MOSFET晶体管可在最高和最低阻抗状态(开通或关断)间切换。四个阶段的长度是寄生电容值、电容上所需的电压变化和可用的栅极驱动电流的函数。这就突显出正确的组件选择以及出色的栅极驱动设计对于高速高频开关 应用非常重要。

遗憾的是,这些数字与特定测试条件和电阻负载相对应,因此难以比较不同制造商的产品。而且,在具有限定电感负载的实际应用中,开关性能与数据表中给出的数字有显著差异。

功率损耗

功率应用中,MOSFET晶体管的开关操作会导致某些不可避免的损耗,具体分为两类。

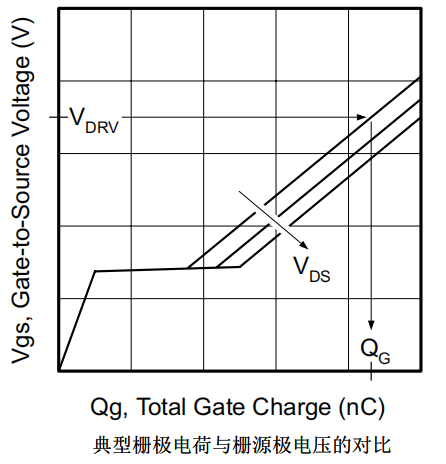

首先,比较简单的一种是器件的栅极驱动损耗。如前面所述,开通或关断MOSFET需要对CISS电容器充电或放电。当电容器上的电压发生变化时,就会转移一定数量的电荷。栅极电压在0V和实际栅极驱动电压VDRV之间变化所需的电荷数量由典型栅极电荷与栅源极电压曲线的对比来表征。

典型栅极电荷与栅源极电压的对比图

可以确定,栅极驱动路径中串联欧姆阻抗的组合是耗能分量。在每个开关周期中,所需的栅极电荷应通过驱动器输出阻抗、外部栅极电阻器和内部栅极网状电阻。实际上,功率损耗与通过电阻器传输电荷的快慢无关。

可以假定,使用低阻值栅极电阻器(<5Ω)时,大多数栅极驱动损耗发生在驱动器中。如果RGATE足够大,可将IG限制在双极驱动器的输出电流能力以下,那么绝大部分栅极驱动功率损耗则发生在RGATE中。

其次,由于器件会在短时间内同时出现高电流和高电压,因此在传统感应中晶体管会累积开关损耗。为了尽可能降低开关损耗,必须尽量减少此阶段的持续时间。看看MOSFET的开关流程,此条件限于开关操作中开关切换的间隔2和间隔3。这些时间间隔对应于栅极电压介于阀值VTH和VGS,Miller之间时器件的线性运行(这会导致器件的电流发生变化),以及漏极电压经历开关切换时的米勒平坦区域。

认识到这一点对于正确设计高速栅极驱动电路来说非常重要。它强调了这一事实:栅极驱动器的最重要特性是米勒平坦区域电压电平周围的拉-灌电流能力。峰值电流能力是通过在完整VDRV下对器件的输出阻抗进行测量的,与MOSFET的实际开关性能关系不大。真正决定器件开关时间的因素是当栅源极电压(即驱动器输出)约为5V(对于逻辑电平MOSFET约为2.5V)时的栅极驱动电流能力。

虽然开关切换很好理解,但几乎仍然无法计算准确的开关损耗。原因是在开关过程中,寄生电感分量的影响会极大地改变电流和电压波形以及开关时间。考虑到实际电路中不同源极电感和漏极电感的影响,本文用二阶微分方程来描述电路的实际波形。由于栅极阀值电压、MOSFET电容值、驱动器输出阻抗等变量具有很大的容差,上述线性近似似乎是非常合理的折衷,可用于估算MOSFET中的开关损耗。

寄生器件的影响

源极电感(LS)对开关性能的影响最大。典型电路中寄生源极电感有两个来源:巧妙集成在MOSFET封装中的源极接合线以及源极引线和共用接地之间的印刷电路板线路电感。这通常是指功率级高频滤波器电容器和栅极驱动器的旁路电容器的负电极。与源极串联的电流感应电阻器可以向之前的两个分量添加更多电感。

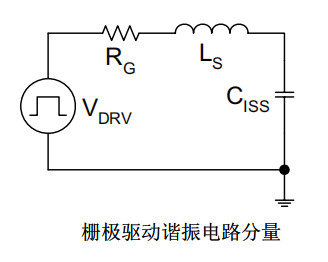

在需要源电感器的开关流程中有两种机制。在开关切换开始时,栅极电流快速增加。此电流必须流经源电感,并根据电感值减小。因此,对MOSFET的输入电容充电/放电所需的时间延长,从而主要对开关延时(第1步)产生影响。而且,源电感器(LS)和CISS电容器会形成一个谐振电路。

栅极驱动谐振电路分量图

此谐振电路在栅极驱动电压波形的陡峭边缘退出,这是在大多数栅极驱动电路中观察到振荡峰值的根本原因。遗憾的是,CISS和源极电感 (LS)之间非常高的Q共振会通过(或可通过)环路的串联电阻分量衰减,这些分量包括驱动器输出阻抗、外部栅极电阻器和内部栅极网状电阻器。需要注意的是,减小电阻值可导致栅极驱动电压波形过冲,还可提高开通速度。电阻值升高会导致振荡欠阻尼并延长开关时间,对于栅极驱动设计没有任何好处。

源极电感的第二个影响是,只要器件的漏极电流快速改变,就会产生负反馈。这种影响出现在开通过程的第二阶段,以及关断过程的第三阶段中。在这些阶段,栅极电压处于阈值VTH和VGS,Miller之间,栅极电流由驱动阻抗上的电压VDRV-VGS定义。为了快速增加漏极电流,必须在源极电感上施加明显的电压。此电压会降低驱动阻抗上的可用电压,从而减小栅极驱动电压的变化率和漏极电流的di/dt。di/dt减小要求源电感上的电压降低。栅极电流和漏极di/dt之间的微妙平衡通过源极电感器的负反馈建立。

开关网络的另一个寄生电感是漏极电感,同样由几个分量构成。它们是晶体管封装中的封装电感、与互连关联的所有电感,以及隔离电源中变压器的泄漏电感。它们串联在一起,因此影响相互叠加。它们充当MOSFET的开通阻尼器。在开通期间,它们限制漏极电流的di/dt,并将器件上的漏源电压降低LD×di/dt倍。

可见,漏极电感 (LD)可以显著降低开通开关损耗,LD值升高似乎对开通有利,但当漏极电流必须快速下降时会拖后腿,导致较大问题。为了支持因MOSFET的关断而快速减小漏极电流,在LD上必须形成与开通所对应的相反方向的电压。此电压高于VDS,off电平的理论值,在漏源电压上形成过冲,并增加关断开关损耗。

实际上,源极电感 (LS) 和漏极电感 (LD) 对开关性能的影响非常复杂。虽然有多种模型可说明MOSFET工作原理,这些模型对于设计人员在实践中遇到的应用陷阱却鲜有提及,几乎所有制造商对于制造出色的功率MOSFET都有自己独特的方法。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍