电子产品生产革命的一项技术是“ 集成电路 ”。该技术通过增加每个芯片的逻辑门密度来减小电子产品的尺寸。今天,我们有不同类型和配置的IC。正如我们在周围观察到的那样,我们发现有些IC仅可用于一种特定的应用,而有些IC可以重新编程并用于各种应用。这些类型的IC称为ASIC。但是它们有何不同?如何对其进行重新编程?为什么有些IC无法重新编程?希望找到这些问题的答案。

什么是ASIC(专用集成电路)?

ASIC的完整形式是“ 专用集成电路”。这些电路是专用的,即为特定应用量身定制的IC。这些通常是根据特定应用程序的要求从根级别设计的。一些特定于应用的基本集成电路示例包括玩具中使用的芯片,用于存储器和微处理器接口的芯片等……这些芯片只能用于设计了这些芯片的那个应用。大概,这些类型的IC仅对那些生产量大的产品是首选。由于ASIC是从根本上设计的,因此它们具有很高的成本,并且仅建议用于批量生产。

ASIC的主要优点是减小了芯片尺寸,因为在单个芯片上构造了电路的大量功能单元。现代ASIC通常包括32位微处理器,存储块,网络电路等。这类ASIC被称为片上系统。随着制造技术的发展和对设计方法的研究的不断发展,具有不同定制级别的ASIC被开发出来。

ASIC类型

ASIC是根据允许程序员在芯片上进行的定制量来分类的。

全定制

在这种类型的设计中,所有逻辑单元都是为特定应用量身定制的,即设计人员必须专门为电路制造逻辑单元。所有用于互连的掩模层都是定制的。因此程序员无法更改芯片的互连,并且在编程时必须了解电路布局。

完全定制ASIC的最佳示例之一是微处理器。这种类型的定制允许设计人员在单个IC上构建各种模拟电路,优化的存储单元或机械结构。该ASIC成本高昂并且制造和设计非常耗时。设计这些IC所需的时间约为八周。

这些通常用于高级应用程序。最大的性能,最小的面积和最高的灵活性是完全定制设计的主要功能。最终,设计中的风险很高,因为未对逻辑单元,电阻器等使用的电路元件进行预测试。

半定制

在这种类型的设计中,逻辑单元是从标准库中获取的,即,它们不是像完全定制设计中那样手工制作的。有些口罩是定制的,有些则是从预先设计的库中提取的。基于从库中获取的逻辑单元的类型以及互连允许的定制量,这些ASIC分为两种类型:基于标准单元的ASIC和基于门阵列的ASIC。

1)基于标准单元的ASIC

首先要了解这些IC,让我们了解标准单元库的含义。某些逻辑单元(例如与门,或门,多路复用器,触发器)由设计人员使用不同的配置进行预先设计,并以库的形式进行标准化和存储。该集合称为标准单元库。

在基于标准单元的标准逻辑库中,使用了这些标准库中的ASIC逻辑单元。在ASIC芯片上,标准单元区域或柔性块由以行形式排列的标准单元组成。连同这些灵活的模块,在芯片上使用大型单元,例如微控制器甚至微处理器。这些兆单元也称为兆功能,系统级宏,固定块,功能标准块。

上图表示具有单个标准单元区域和四个固定块的标准单元ASIC。遮罩层是自定义的。设计人员可以在此处将标准单元放置在管芯上的任何位置。这些也称为C-BIC。

2)基于门阵列的ASIC

这种类型的半定制ASIC 在硅晶圆上具有预定义的晶体管,即设计人员无法更改管芯上存在的晶体管的位置。基本阵列是门阵列的预定义模式,基本单元是基本阵列中最小的重复单元。

设计人员仅负责使用管芯的前几个金属层来改变晶体管之间的互连。设计人员从门阵列库中进行选择。这些通常称为“屏蔽门阵列”。基于门阵列的ASIC有三种类型。它们是通道化门阵列,无通道门阵列和结构化门阵列。

a)通道门阵列

在这种类型的门阵列中,在晶体管行之间留有布线空间。这些类似于CBIC,因为在块之间保留了用于互连的空间,但在通道式门阵列单元行中的高度固定,而在CBIC中,此空间可以调整。

该门阵列的一些主要特征是-该门阵列使用行之间的预定义空间进行互连。制造时间为两天到两周。

b)无通道门阵列

如通道门阵列中所示,在单元的行之间没有用于路由的剩余空间。这里的布线是从门阵列单元上方进行的,因为我们可以自定义金属1和晶体管之间的连接。对于布线,我们不用使用位于布线路径中的晶体管。生产准备时间约为两周。

c)结构化门阵列

如上所示,这种类型的门阵列具有嵌入式块以及门阵列行。结构化门阵列具有较高的CBIC面积效率。像屏蔽门阵列一样,它们具有较低的成本和更快的周转时间。在此,嵌入式功能的固定大小会限制结构化门阵列。例如,此门阵列是否包含为32k位控制器保留的区域,但是如果在应用程序中我们仅需要16k位控制器的区域,则剩余区域将被浪费。所有门阵列的周转时间为两天到两周,并且全部都有定制的互连。

专用集成电路(ASIC)设计流程

逐步设计ASIC。此步骤顺序称为ASIC设计流程。下面的流程图中给出了设计流程的步骤。

设计输入:在此步骤中,使用诸如VHDL,Verilog和System Verilog之类的硬件描述语言来实现设计的微体系结构。

逻辑综合:在此步骤中,将使用HDL准备要使用的逻辑单元的网表,互连的类型以及应用程序所需的所有其他部件。

系统分区:在这一步,我们将大型裸片划分为ASIC裸片。

布局前仿真:在此步骤中,进行仿真测试以检查设计是否包含任何错误。

平面规划:在此步骤中,将网表块安排在芯片上。

放置:在此步骤中,确定块内单元的位置。

路由:在此步骤中,将在块和单元之间绘制连接。

提取:在此步骤中,我们确定电性能,例如电阻值和互连的电容值。

布局后仿真:在提交用于制造的模型之前,需要完成此仿真,以检查系统是否正常运行以及互连负载。

ASIC的优缺点

ASIC的优点如下:

1、 ASIC的小尺寸使其成为复杂的大型系统的理想选择。

2、由于在单个芯片上构建了大量电路,这导致了高速应用。

3、 ASIC具有低功耗。

4、 由于它们是芯片上的系统,因此电路并排存在。因此,连接? 各种电路所需的布线极少。

5、ASIC没有时序问题和后期制作配置。

ASIC的缺点如下:

1、 由于这些是定制芯片,因此它们的编程灵活性较低。

2、 由于必须从根本上设计这些芯片,因此它们的单位成本较高。

3、ASIC拥有更大的上市时间。

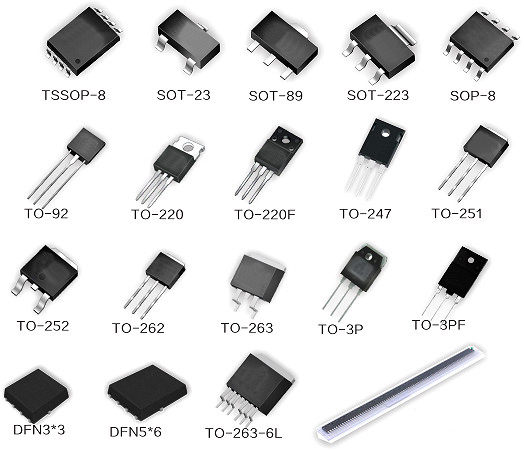

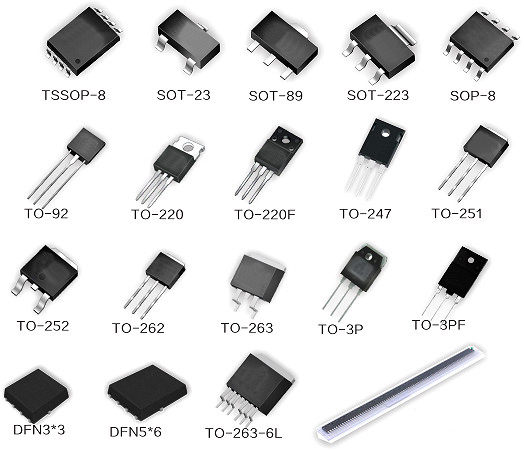

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍