半导体封装技术

本文主要讲半导体封装技术,电子封装是集成电路芯片生产完成后不可缺少的一道工序,是器件到系统的桥梁。封装这一生产环节对微电子产品的质量和竞争力都有极大的影响。按目前国际上流行的看法认为,在微电子器件的总体成本中,设计占了三分之一,芯片生产占了三分之一,而封装和测试也占了三分之一,真可谓三分天下有其一。

什么是封装

半导体封装技术,先看看封装最初的定义是保护电路芯片免受周围环境的影响(包括物理、化学的影响)。

芯片封装是利用(膜技术)及(微细加工技术),将芯片及其他要素在框架或基板上布置、粘贴固定及连接,引出接线端子并通过可塑性绝缘介质灌封固定,构成整体结构的工艺。

电子封装工程:将基板、芯片封装体和分立器件等要素,按电子整机要求进行连接和装配,实现一定电气、物理性能,转变为具有整机或系统形式的整机装置或设备。

集成电路封装能保护芯片不受或者少受外界环境的影响,并为之提供一个良好的工作条件,以使集成电路具有稳定、正常的功能。

芯片封装能实现电源分配;信号分配;散热通道;机械支撑;环境保护。

半导体封装技术发展阶段详解

从Foundry厂得到圆片进行减薄、中测打点后,即可进入后道封装。封装对集成电路起着机械支撑和机械保护、传输信号和分配电源、散热、环境保护等作用。

随着集成电路的迅速发展,IC封装技术也随着提高,IC行业应用需求越来越大,集成度也越来越高,技术指标一代比一代先进,芯片面积与封装面积比例越来越接近1,电器性能以及可靠性也逐渐提高,体积更加小型化和薄型化。

半导体行业对芯片封装技术水平的划分存在不同的标准,目前国内比较通行的标准是采取封装芯片与基板的连接方式来划分,总体来讲,集成电路封装封装技术的发展可分为四个阶段:

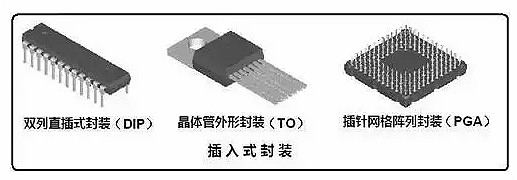

第一阶段:20世纪80年代以前(插孔原件时代)

封装的主要技术是针脚插装(PTH),其特点是插孔安装到PCB上,主要形式有SIP、DIP、PGA,它们的不足之处是密度、频率难以提高,难以满足高效自动化生产的要求。

TO(晶体管外形封装)

TO是晶体管外形封装,一类是晶体管封装类,这种能够使引线被表面贴装,另一类是圆形金属外壳封装无表面贴装部件类。这种封装应用很广泛,很多三极管、MOS管、晶闸管等均采用这种封装。

DIP(双列封装)

DIP封装也叫双列直插式封装或者双入线封装,绝大多数中小规模集成电路均采用这种封装形式,其引脚数一般不超过100,采用这种封装方式的芯片有两排引脚,可以直接焊在有DIP结构的芯片插座上或焊在有相同焊孔数的焊位中。其特点是可以很方便地实现PCB板的穿孔焊接,和主板有很好的兼容性。包括CerDIP(陶瓷双列直插式封装)、PDIP(塑封)。

SIP(单列直插封装)

单列直插式封装引脚从封装一个侧面引出,排列成一条直线。通常它们是通孔式的,引脚从封装一个侧面引出,排列成一条直线。当装配到印刷基板上时封装呈侧立状。引脚中心距通常为2.54mm,引脚数从2 至23,多数为定制产品。封装的形状各异。

PGA(引脚栅阵列)

陈列引脚封装。插装型封装之一,其底面的垂直引脚呈陈列状排列。封装基材基本上都采用多层陶瓷基板。用于高速大规模逻辑LSI电路。管脚在芯片底部,一般为正方形,引脚中心距通常为2.54mm,引脚数从64到447左右。一般有CPGA(陶瓷针栅阵列封装)以及PPGA(塑料针栅阵列封装)两种。

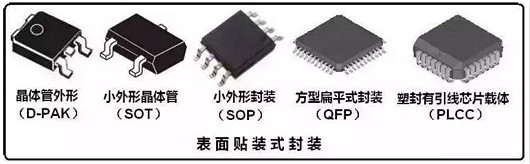

第二阶段:20世纪80年代中期(表面贴装时代)

表面贴装封装的主要特点是引线代替针脚,引线为翼形或丁形,两边或四边引出,节距为1.27到0.4mm,适合于3-300条引线,表面贴装技术改变了传统的PTH插装形式,通过细微的引线将集成电路贴装到PCB板上。主要形式为SOP(小外型封装)、PLCC(塑料有引线片式载体)、PQFP(塑料四边引线扁平封装)、J型引线QFJ和SOJ、LCCC(无引线陶瓷芯片载体)等。

它们的主要优点是引线细、短,间距小,封装密度提高;电气性能提高;体积小,重量轻;易于自动化生产。它们所存在的不足之处是在封装密度、I/O数以及电路频率方面还是难以满足ASIC、微处理器发展的需要。

SOP(小型封装)

SOP封装是一种元件封装形式,常见的封装材料有:塑料、陶瓷、玻璃、金属等,现在基本采用塑料封装.,应用范围很广,主要用在各种集成电路中。后面就逐渐有TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)、

MSOP(微型外廓封装)、 QSOP(四分之一尺寸外形封装)、QVSOP(四分之一体积特小外形封装)等封装。

LCC(带引脚或无引脚芯片载体)

带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,是高速和高频IC用封装,也称为陶瓷QFN或QFN-C。有CLCC(翼形引脚)、LDCC、PLCC。

QFP (四方扁平封装)

这种封装是方型扁平式封装,一般为正方形,四边均有管脚,采用该封装实现的CPU芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。因其其封装外形尺寸较小,寄生参数减小,适合高频应用。这类封装有:CQFP(陶瓷四方扁平封装)、 PQFP(塑料四方扁平封装)、SSQFP(自焊接式四方扁平封装)、TQFP(纤薄四方扁平封装)、SQFP(缩小四方扁平封装)。

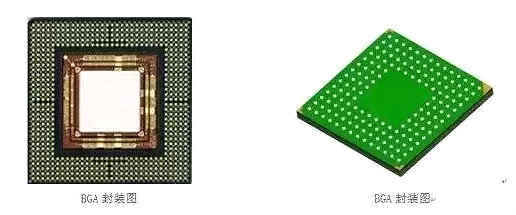

第三阶段:20世纪90年代出现了第二次飞跃,进入了面积阵列封装时代

该阶段主要的封装形式有焊球阵列封装(BGA)、芯片尺寸封装(CSP)、无引线四边扁平封装(PQFN)、多芯片组件(MCM)。BGA技术使得在封装中占有较大体积和重量的管脚被焊球所替代,芯片与系统之间的连接距离大大缩短,BGA技术的成功开发,使得一直滞后于芯片发展的封装终于跟上芯片发展的步伐。CSP技术解决了长期存在的芯片小而封装大的根本矛盾,引发了一场集成电路封装技术的革命。

MCM(多芯片组件)

其实这是一种芯片组件,是一种最新技术,它是将多块半导体裸芯片组装在一块布线基板上的一种封装技术,因此它省去了IC的封装材料和工艺,从而节省了材料,同时减少了必要的制造工艺,因此严格的是一种高密度组装产品。

CSP (芯片规模封装)

CSP封装是一种芯片级封装,我们都知道芯片基本上都是以小型化著称,因此CSP封装最新一代的内存芯片封装技术,可以让芯片面积与封装面积之比超过1:1.14,已经相当接近1:1的理想情况,被行业界评为单芯片的最高形式,与BGA封装相比,同等空间下CSP封装可以将存储容量提高三倍。这种封装特点是体积小、输入/输出端数可以很多以及电气性能很好,有CSP BGA(球栅阵列)、LFCSP(引脚架构)、LGA(栅格阵列)、WLCSP(晶圆级)等。

BGA (球栅阵列)

球形触点阵列,表面贴装型封装之一。在印刷基板的背面按陈列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI 芯片,然后用模压树脂或灌封方法进行密封。也称为凸点陈列载体(PAC)。BGA主要有:PBGA(塑料封装的BGA)、CBGA(陶瓷封装的BGA)、CCBGA(陶瓷柱状封装的BGA)、TBGA(载带状封装的BGA)等。目前应用的BGA封装器件, 按基板的种类,主要CBGA(陶瓷球栅阵列封装)、 PBGA(塑料球栅阵列封装)、TBGA(载带球栅阵列封装)、FC-BGA(倒装球栅阵列封装)、EPBG(增强的塑胶球栅阵列封装)等。

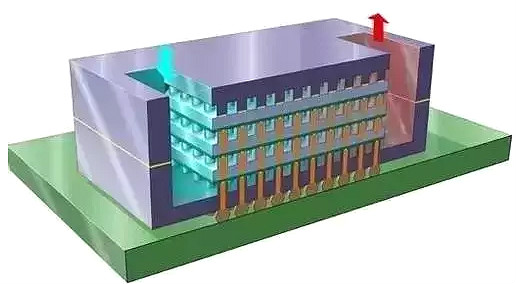

第四阶段:进入21世纪,迎来了微电子封装技术堆叠式封装时代,它在封装观念上发生了革命性的变化,从原来的封装元件概念演变成封装系统。

3D晶片堆叠技术

堆叠式存储模块

目前,以全球半导体封装的主流正处在第三阶段的成熟期,PQFN和BGA等主要封装技术进行大规模生产,部分产品已开始在向第四阶段发展。

半导体封装技术的封装工艺流程

1.封装工艺流程 一般可以分为两个部分,用塑料封装之前的工艺步骤成为前段操作,在成型之后的工艺步骤成为后段操作。

2.芯片封装技术的基本工艺流程 硅片减薄 硅片切割 芯片贴装,芯片互联 成型技术 去飞边毛刺 切筋成型 上焊锡打码等工序。

3.硅片的背面减薄技术主要有磨削,研磨,化学机械抛光,干式抛光,电化学腐蚀,湿法腐蚀,等离子增强化学腐蚀,常压等离子腐蚀等。

4.先划片后减薄:在背面磨削之前将硅片正面切割出一定深度的切口,然后再进行背面磨削。

5.减薄划片:在减薄之前,先用机械或化学的方式切割处切口,然后用磨削方法减薄到一定厚度之后采用ADPE腐蚀技术去除掉剩余加工量实现裸芯片的自动分离。

6.芯片贴装的方式四种:共晶粘贴法,焊接粘贴法,导电胶粘贴法,和玻璃胶粘贴法。

共晶粘贴法:利用金-硅合金(一般是69%Au,31%的Si),363度时的共晶熔合反应使IC芯片粘贴固定。

7.为了获得最佳的共晶贴装所采取的方法,IC芯片背面通常先镀上一层金的薄膜或在基板的芯片承载座上先植入预芯片。

8.芯片互连常见的方法有,打线键合,载在自动键合(TAB)和倒装芯片键合。

9.打线键合技术有,超声波键合,热压键合,热超声波键合。

10.TAB的关键技术:1芯片凸点制作技术2TAB载带制作技术3载带引线与芯片凸点的内引线焊接和载带外引线焊接技术。

11.凸点芯片的制作工艺,形成凸点的技术:蒸发/溅射涂点制作法,电镀凸点制作法置球及模板印刷制作,焊料凸点发,化学镀涂点制作法,打球凸点制作法,激光法。

12.塑料封装的成型技术,1转移成型技术,2喷射成型技术,3预成型技术但最主要的技术是转移成型技术,转移技术使用的材料一般为热固性聚合物。

13.减薄后的芯片有如下优点:

1、薄的芯片更有利于散热;

2、减小芯片封装体积;

3、提高机械性能、硅片减薄、其柔韧性越好,受外力冲击引起的应力也越小;

4、晶片的厚度越薄,元件之间的连线也越短,元件导通电阻将越低,信号延迟时间越短,从而实现更高的性能;

5、减轻划片加工量减薄以后再切割,可以减小划片加工量,降低芯片崩片的发生率。

14. 波峰焊:波峰焊的工艺流程包括上助焊剂、预热以及将PCB板在一个焊料波峰上通过,依靠表面张力和毛细管现象的共同作用将焊剂带到PCB板和元器件引脚上,形成焊接点。 波峰焊是将熔融的液态焊料,借助于泵的作用,在焊料槽液面形成特定形状的焊料波,装了元器件的PCB置于传送链上,经某一特定的角度以及一定的进入深度穿过焊料波峰而实现焊点的焊接过程。

再流焊:是通过预先在PCB焊接部位施放适量和适当形式的焊料,然后贴放表面组装元器件,然后通过重新熔化预先分配到印制板焊盘上的焊膏,实现表面组装元器件焊端或引脚与印制板焊盘之间机械与电气连接的一种成组或逐点焊接工艺。

15.打线键合(WB):将细金属线或金属带按顺序打在芯片与引脚架或封装基板的焊垫上形成电路互连。打线键合技术有超声波键合、热压键合、热超声波键合。载带自动键合(TAB):将芯片焊区与电子封装外壳的I/O或基板上的金属布线焊区用具有引线图形金属箔丝连接的技术工艺。倒装芯片键合(FCB):芯片面朝下,芯片焊区与基板焊区直接互连的一种方法。

16. 芯片互连:将芯片焊区与电子封装外壳的I/O或基板上的金属布线焊区相连接,只有实现芯片与封装结构的电路连接才能发挥已有的功能。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍