什么是power mosfet

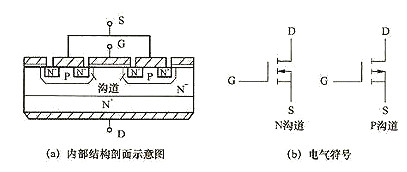

power mosfet,中文是电力场效应晶体管的意思。电力场效应晶体管分为两种类型,结型和绝缘栅型,但通常所说的是绝缘栅型中的MOS型(Metal Oxide Semiconductor FET),简称电力MOSFET(Power MOSFET)。

P-MOSFET是用栅极电压来控制漏极电流,它的显著特点是驱动电路简单,驱动功率小,开关速度快,工作频率高;但是其电流容量小,耐压低,只用于小功率的电力电子装置,其工作原理与普通MOSFET一样。

特性

power mosfet的主要特性如下:power mosfet静态特性主要指输出特性和转移特性, 与静态特性对应的主 要参数有漏极击穿电压,漏极额定电压,漏极额定电流和栅极开启电压等.

1、静态特性

(1) 输出特性 输出特性即是漏极的伏安特性.特性曲线,如图 2(b)所示.由图所见,输出 特性分为截止,饱和与非饱和 3 个区域.这里饱和,非饱和的概念与 GTR 不同. 饱和是指漏极电流 ID 不随漏源电压 UDS 的增加而增加,也就是基本保持不变;非 饱和是指地 UCS 一定时,ID 随 UDS 增加呈线性关系变化.

(2) 转移特性 转移特性表示漏极电流 ID 与栅源之间电压 UGS 的转移特性关系曲线, 如图 2(a) 所示. 转移特性可表示出器件的放大能力, 并且是与 GTR 中的电流增益 β 相似. 由于power mosfet是压控器件,因此用跨导这一参数来表示.跨导定义为 (1) 图中 UT 为开启电压,只有当 UGS=UT 时才会出现导电沟道,产生漏极电流 ID

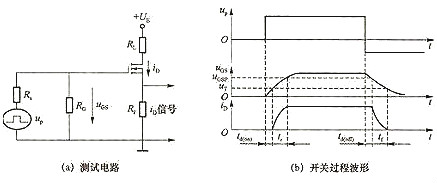

2、动态特性

动态特性主要描述输入量与输出量之间的时间关系,它影响器件的开关过程.由于该器件为单极型,靠多数载流子导 电,因此开关速度快,时间短,一般在纳秒数量级.

power mosfet的动态特性.如图所示.

power mosfet栅极电阻;RL 为漏极负载电阻;RF 用以检测漏极 电流.power mosfet的开关过程波形,如图 3(b)所示. power mosfet的开通过程:由于 Power MOSFET 有输入电容,因此当脉 冲电压 up 的上升沿到来时,输入电容有一个充电过程,栅极电压 uGS 按指数曲线 上升.当 uGS 上升到开启电压 UT 时,开始形成导电沟道并出现漏极电流 iD.从 up 前沿时刻到 uGS=UT,且开始出现 iD 的时刻,这段时间称为开通延时时间 td(on).此 后,iD 随 uGS 的上升而上升,uGS 从开启电压 UT 上升到power mosfet临近饱和区 的栅极电压 uGSP 这段时间,称为上升时间 tr.这样power mosfet的开通时间

ton=td(on)+tr(2)

power mosfet 的关断过程:当 up 信号电压下降到 0 时,栅极输入电容上储 存的电荷通过电阻 RS 和 RG 放电,使栅极电压按指数曲线下降,当下降到 uGSP 继 续下降,iD 才开始减小,这段时间称为关断延时时间 td(off).此后,输入电容继续 放电,uGS 继续下降,iD 也继续下降,到 uGST 时导电沟道消失,iD=0, 这段时间称为下降时间 tf.这样 Power MOSFET 的关断时间

toff=td(off)+tf (3)

从上述分析可知,要提高器件的开关速度,则必须减小开关时间.在输入电 容一定的情况下,可以通过降低驱动电路的内阻 RS 来加快开关速度. 电力场效应管晶体管是压控器件,在静态时几乎不输入电流.但在开关过程 中,需要对输入电容进行充放电,故仍需要一定的驱动功率.工作速度越快,需 要的驱动功率越大。

主要参数

power mosfet的主要参数

除跨导Gfs、开启电压UT以及td(on)、tr、td(off)和tf之外还有:

(1)漏极电压UDS——电力MOSFET电压定额

(2)漏极直流电流ID和漏极脉冲电流幅值IDM——电力MOSFET电流定额

(3)栅源电压UGS—— UGS>20V将导致绝缘层击穿 。

(4)极间电容——极间电容CGS、CGD和CDS

间加正向电压使N型半导体中的多数载流子-电子由源极出发,经过沟道到达漏极形成漏极电流ID。

power mosfet结构、原理、正向导通解析

所谓功率MOS就是要承受大功率,换言之也就是高电压、大电流。我们结合一般的低压MOSFET来讲解如何改变结构实现高压、大电流。

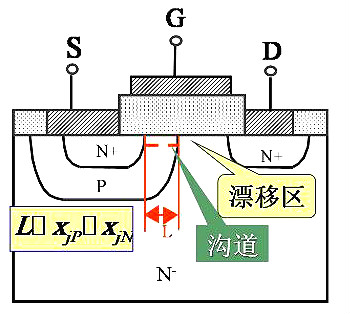

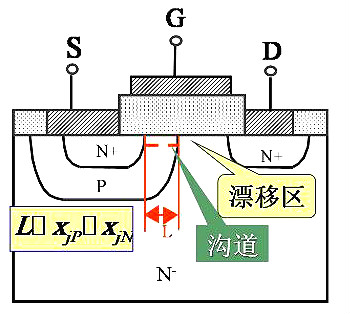

1) 高电压:一般的MOSFET如果Drain的高电压,很容易导致器件击穿,而一般击穿通道就是器件的另外三端(S/G/B),所以要解决高压问题必须堵死这三端。Gate端只能靠场氧垫在Gate下面隔离与漏的距离(Field-Plate),而Bulk端的PN结击穿只能靠降低PN结两边的浓度,而最讨厌的是到Source端,它则需要一个长长的漂移区来作为漏极串联电阻分压,使得电压都降在漂移区上就可以了。

2) 大电流:一般的MOSFET的沟道长度有Poly CD决定,而功率MOSFET的沟道是靠两次扩散的结深差来控制,所以只要process稳定就可以做的很小,而且不受光刻精度的限制。而器件的电流取决于W/L,所以如果要获得大电流,只需要提高W就可以了。

虽然这样的器件能够实现大功率要求,可是它依然有它固有的缺点,由于它的源、栅、漏三端都在表面,所以漏极与源极需要拉的很长,太浪费芯片面积。而且由于器件在表面则器件与器件之间如果要并联则复杂性增加而且需要隔离。

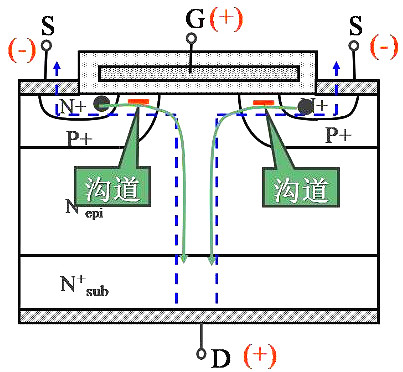

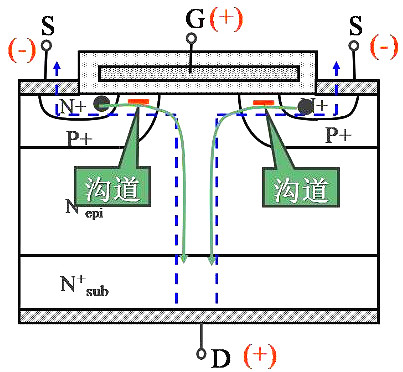

所以后来发展了VDMOS(Vertical DMOS),把漏极统一放到Wafer背面去了,这样漏极和源极的漂移区长度完全可以通过背面减薄来控制,而且这样的结构更利于管子之间的并联结构实现大功率化。但是在BCD的工艺中还是的利用LDMOS结构,为了与CMOS兼容。

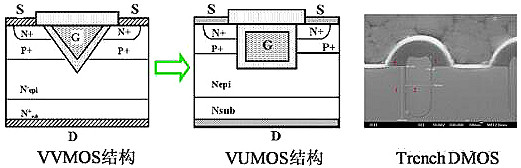

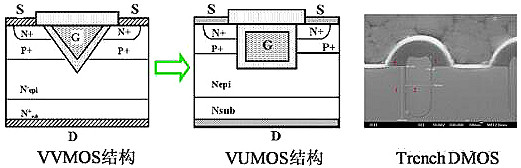

再给大家讲一下VDMOS的发展及演变吧,最早的VDMOS就是直接把LDMOS的Drain放到了背面通过背面减薄、Implant、金属蒸发制作出来的(如下图),他就是传说中的Planar VDMOS,它和传统的LDMOS比挑战在于背面工艺。但是它的好处是正面的工艺与传统CMOS工艺兼容,所以它还是有生命力的。但是这种结构的缺点在于它沟道是横在表面的,面积利用率还是不够高。

再后来为了克服Planar DMOS带来的缺点,所以发展了VMOS和UMOS结构。他们的做法是在Wafer表面挖一个槽,把管子的沟道从原来的Planar变成了沿着槽壁的vertical,果然是个聪明的想法。但是一个馅饼总是会搭配一个陷阱(IC制造总是在不断trade-off),这样的结构天生的缺点是槽太深容易电场集中而导致击穿,而且工艺难度和成本都很高,且槽的底部必须绝对rouding,否则很容易击穿或者产生应力的晶格缺陷。但是它的优点是晶饱数量比原来多很多,所以可以实现更多的晶体管并联,比较适合低电压大电流的application。

power mosfet注意事项

1、防止静电击穿

防止静电击穿时应注意:

(1)在MOSFET测试和接人电路之前,应存放在静电包装袋、导电材料或金属容器中,不能放在塑料盒或塑料袋中。取用时应拿管壳部分而不是引线部分。工作人员需通过腕带良好接地。

(2)将MOSFET接入电路时,工作台和烙铁都必须良好接地,焊接时电烙铁功率应不超过25W,最好是用内热式烙铁。先焊栅极,后焊漏极与源极。

(3)在测试MOSFET时,测量仪器和工作台都必须良好接地,并尽量减少相同仪器的使用次数和使用时间,从而尽快作业。MOsFET的三个电极未全部接入测试仪器或电路前.不要施加电压。改换测试范围时,电压和电流都必须先恢复到零。

(4)注意栅极电压不要过限。有些型号的电力MOSFET内部输入端接有齐纳保护二极管,这种器件栅源间的反向电压不得超过0.3V,对于内部未设齐纳保护:极管的器件,应在栅源同外接齐纳保护二极管或外接其他保护电路。

(5)使用MOSFET时,尽最不穿易产生静电荷的服装(如尼龙服装)。

(6)在操作现场,要尽量回避易带电的绝缘体(特别是化学纤维和靼料易带电)和使用导电性物质。例如:导电性底板、空气离子化增压器等,并避免操作现场放置易产生静电的物质,保证操作现场湿度适当。当湿度过高时,可采取加温措施,正确的操作现场防静电措施。

2、防止偶然性振荡损坏器件

电力MOSFET在与测试仪器、接插盒等仪器的输入电容、输入电阻匹配不当时,可能出现偶然性振荡,造成器件损坏。因此,在用图示仪等仪器测试时,在器件的栅极端子处接lOkfl串联电阻,也可在栅源问外接约0.5妒的电容器。

(1)场效应晶体管互导大小与工作区有关,电压越低则越高。

(2)结型场效应晶体管的豫、漏极可以互换使用。

(3)绝缘栅型场效应晶体管.在栅极开路时极易受周围磁场作用,会产生瞬问高电压使栅极击穿。故在存放时,应将三个引脚短路,防止静电感应电荷击穿绝缘栅。

(4)工作点的选择,应不得超过额定漏源电压、栅源电压、耗散功率及最大电流所允许的数值。

(5)测试绝缘栅场效应晶体管时,测试仪器应良好接地,以免击穿栅极。

(6)需采取防潮措施,防止由于输入阻抗下降造成场效应晶体管性能恶化。

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍

烜芯微专业制造二极管,三极管,MOS管,桥堆等20年,工厂直销省20%,1500家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以点击右边的工程师,或者点击销售经理给您精准的报价以及产品介绍