短沟道效应解析

在 MOS 晶体管领域,当沟道长度缩至与漏结及源结耗尽层厚度相近时,一系列有别于长沟道 MOS 管特性的现象便会显现,这些现象被统称为短沟道效应,其根源在于沟道区二维电势分布的形成以及高电场的出现。

当 MOSFET 的沟道长度低于 3 微米时,短沟道效应便较为突出。此类效应的产生主要受以下五种因素影响,这些因素皆源于理想按比例缩小理论的偏离:

一是电源电压未能按比例缩小,致使电场强度增大。

二是内建电势既无法按比例缩小,又不可忽视。

三是源漏结深难以按比例减小。

四是衬底掺杂浓度的上升造成载流子迁移率降低。

五是亚阈值斜率无法按比例缩小。

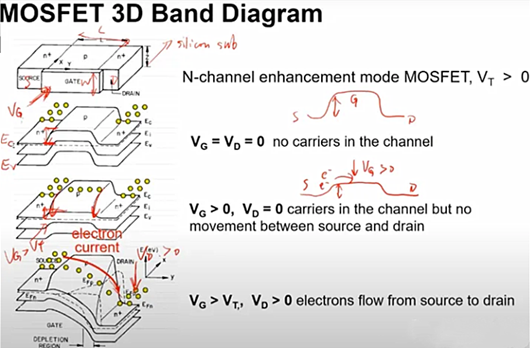

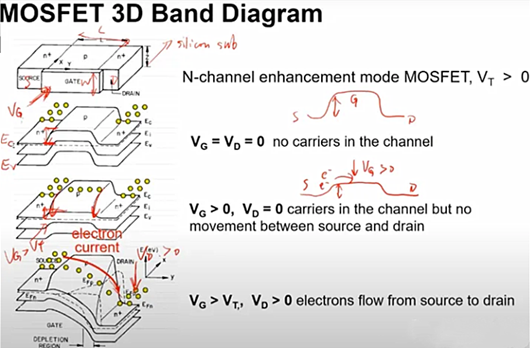

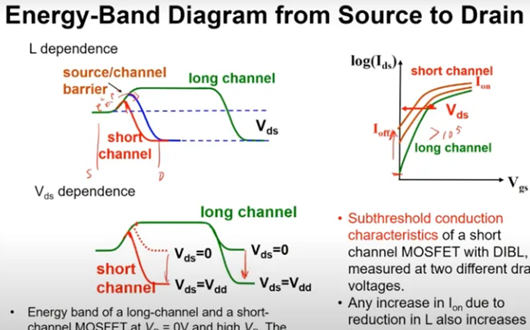

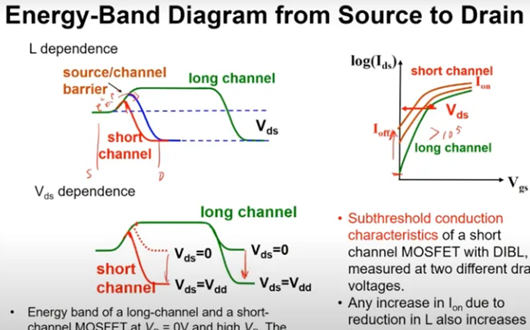

以下借助 MOSFET 3D 能带图,深入剖析短沟道效应。以 NMOS 为例,当施加 Vgs 电压时,在 Gate 表面,能带向下弯曲(如图第三个图例所示),这使得电子更易穿越沟道。然而,由于此时 Drain 尚未加压,能带位置保持不变,因此并无电流流过。

一旦给 Drain 加压(对应图中第四个图例),Drain 处能带向下弯曲,从 Source 经 Channel 至 Drain 形成能级差,电子得以沿此路径流动。

从能带图视角审视短沟道效应,可得出以下结论:

对于短沟道(L 极小)的 MOS 管,Source 与 Drain 距离过近,Channel 能带被向下拉,使得处于 Cut-Off 状态的器件 leakage 增大。这是因为沟道势垒降低,热激发电子在常温下更易越过势垒,从 Source 漂移到 Drain,这一效应显著影响亚阈值漏电流。

若提升 Vds 值,由于 Source 与 Drain 距离过近,Drain 势垒下降会引发 Channel 势垒降低,导致沟道电流 Id 对 Vds 的敏感性增强,这便是所谓的漏诱生势垒降低效应(DIBL)。

因此,若要借助减小沟道 L 值来提升开启电流,需警惕短沟道效应致使 MOS 管关断电流呈指数级增长的风险。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280