开漏输出解析

一、开漏与开集输出

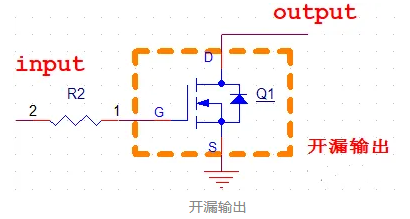

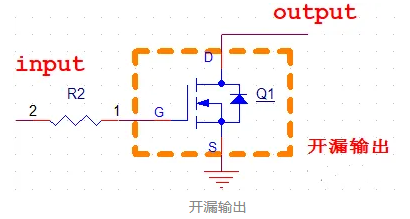

在电子电路设计中,开漏(OD)输出和开集(OC)输出是两种常见的输出配置。当使用 MOS 管作为输出器件时,被称为开漏输出,其输出引脚即为 MOS 管的漏极。

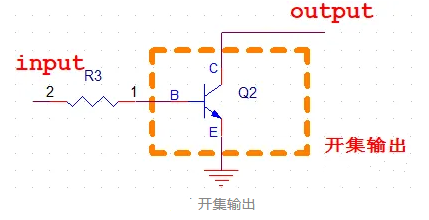

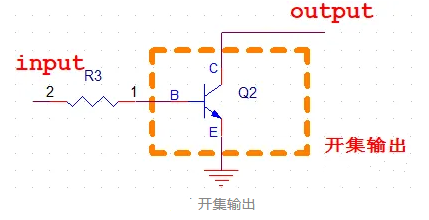

而当以三极管作为输出器件时,则称为开集输出,输出引脚为三极管的集电极。由于 MOS 管在众多应用场景中更为普遍,因此通常使用 “开漏输出” 这一术语来泛指这两种输出方式。

而当以三极管作为输出器件时,则称为开集输出,输出引脚为三极管的集电极。由于 MOS 管在众多应用场景中更为普遍,因此通常使用 “开漏输出” 这一术语来泛指这两种输出方式。

二、开漏输出的特性

(一)高电平需外部驱动

开漏输出最显著的特性之一是其在输出高电平时缺乏自身的驱动能力。这意味着仅依靠开漏输出电路本身,无法直接提供稳定的高电平信号。为解决这一问题,需在漏极或集电极外部接入上拉电阻,连接至相应的电源电平。通过上拉电阻,当输出器件截止时,外部电源可通过上拉电阻为输出端提供高电平,从而使开漏输出具备完整的高低电平输出功能。

(二)电平调节的灵活性

开漏输出的另一大优势在于其输出电平的灵活性。输出电平的高低完全由上拉电阻所连接的电源电压决定。这一特性使得开漏输出在不同电平系统之间进行接口连接时极为便利,尤其是在需要进行电平转换的场合。例如,在将低电压的微控制器与高电压的外围设备进行连接时,只需调整上拉电阻的电源电压,即可实现电平的匹配,而无需复杂的电平转换电路。

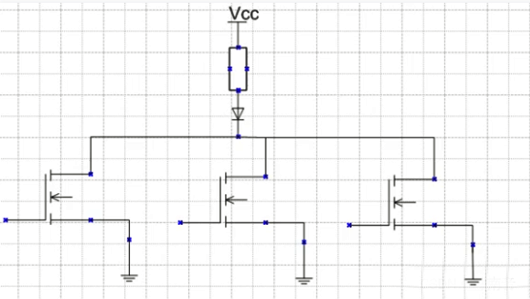

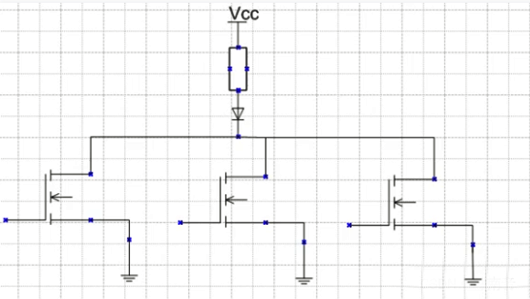

(三)便于实现 “线与” 逻辑

开漏输出在数字逻辑电路中,为实现 “线与” 逻辑功能提供了极大的便利。所谓 “线与”,是指将多个信号线直接连接在一起,形成一条总线。在这种连接方式下,只有当所有连接的信号线输出均为低电平时,总线呈现高电平;只要有一个或多个信号线输出为高电平,总线则呈现低电平。多个开漏输出信号连接到同一条总线上时,可通过各自的输出状态共同决定总线的电平状态,从而实现 “线与” 逻辑功能,这在如 I2C 总线等多主多从通信协议中得到了广泛应用。

三、开漏输出电路原理与应用

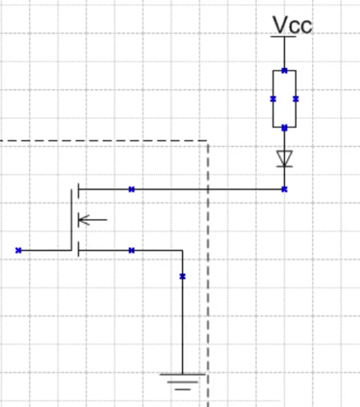

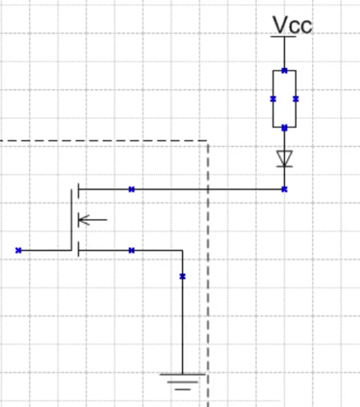

(一)电路结构

开漏输出电路的核心是将场效应管的漏极直接引出作为输出引脚。场效应管在电路中通常工作在饱和区或截止区。当需要输出低电平时,场效应管导通,将输出引脚拉低至接近地电位;当需要输出高电平时,场效应管截止,此时输出引脚处于高阻态,由外部上拉电阻和电源共同作用提供高电平。

(二)电平匹配功能

在实际电路设计中,不同芯片或设备的逻辑电平往往存在差异。例如,某些微控制器的工作电压可能为 3.3V,而与其连接的外围设备可能需要 5V 的逻辑电平。在这种情况下,开漏输出模式能够发挥其电平匹配的优势。通过选择适当的外部上拉电源电压,可以将开漏输出的高电平转换为目标电平,从而实现不同电平系统之间的无缝连接。

(三)减轻 MCU 负担

从微控制器单元(MCU)的角度来看,使用开漏输出模式能够有效减轻其负担。由于开漏输出的高电平由外部电源提供,MCU 无需直接驱动输出引脚至高电平,从而降低了 MCU 的驱动电流需求,有助于提高整个系统的稳定性和可靠性。

(四)“线与” 逻辑的应用实例

在 I2C 总线通信中,多个设备共享同一条数据总线。每个设备的开漏输出引脚连接到该总线上。当某个设备需要发送低电平时,其开漏输出的场效应管导通,将总线拉低;而当所有设备均不发送低电平(即场效应管均截止)时,总线通过上拉电阻连接到电源,呈现高电平。通过这种方式,多个设备可以在总线上进行协同通信,实现数据的传输与共享。这种 “线与” 逻辑的实现方式,使得 I2C 总线能够在简单的硬件基础上,支持多设备通信,降低了硬件成本和复杂度。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280