mos管上拉电阻与下拉电阻区别详解

在电子电路设计领域,上拉电阻与下拉电阻是两种基础却极为关键的元件,它们在电路中扮演着至关重要的角色,主要作用是将不确定的电平信号固定为稳定的高电平或低电平,确保电路的稳定运行。

在电子电路设计领域,上拉电阻与下拉电阻是两种基础却极为关键的元件,它们在电路中扮演着至关重要的角色,主要作用是将不确定的电平信号固定为稳定的高电平或低电平,确保电路的稳定运行。

一、基础概念

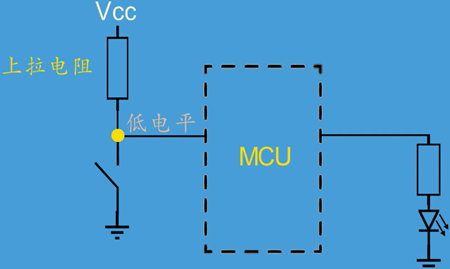

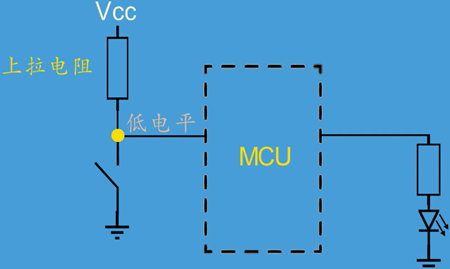

(一)上拉电阻

上拉电阻通过将一个不确定信号与电源 VCCQ 相连,利用电阻将电平稳定在高电平状态。其原理是当电路中存在不确定信号时,电流通过电阻从电源流向信号端,从而使信号端的电平被 “拉高” 至接近电源电压的高电平。这种上拉操作实际上是向器件注入电流,为电路提供稳定的高电平信号。当一个带有上拉电阻的 IO 端口设置为输入状态时,其常态表现为高电平,这是因为上拉电阻持续将信号端维持在高电平状态,除非有其他外部因素(如下拉电路或低电平信号源)将其电平拉低。

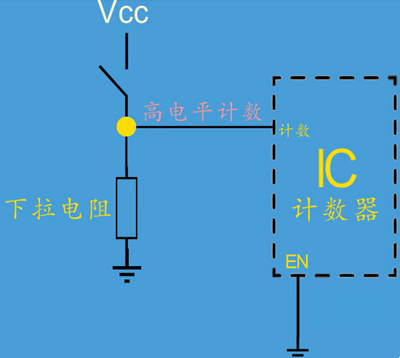

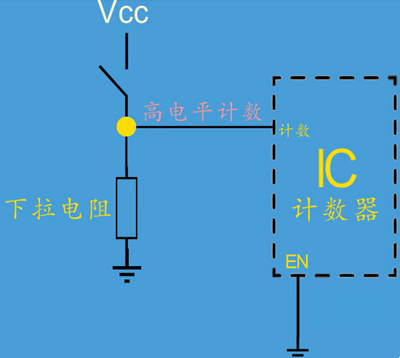

(二)下拉电阻

下拉电阻则是将不确定信号与地 GND 相连,通过电阻将电平固定在低电平。当信号端存在不确定信号时,电流从信号端流向地,从而使信号端的电平被 “拉低” 至接近地电平的低电平状态。下拉电阻的作用是从器件输出电流,确保信号端在无其他驱动因素时保持低电平。带有下拉电阻的 IO 端口在设置为输入状态时,常态呈现低电平,因为下拉电阻持续将信号端电平拉低,除非有外部因素(如上拉电路或高电平信号源)将其电平拉高。

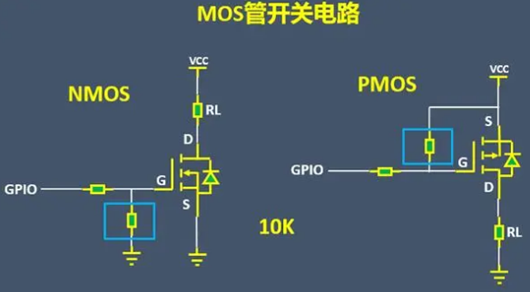

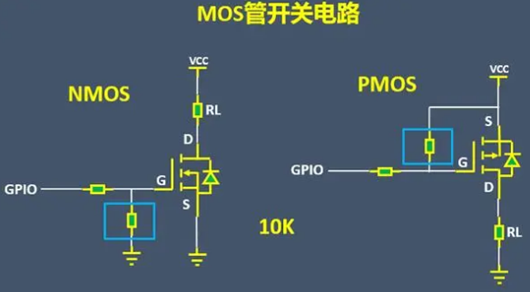

二、MOS 管开关电路中的应用

在 MOS 管开关电源电路中,上拉电阻和下拉电阻有着特定的使用场景和重要作用。

(一)应用场景

当遇到前级电路输出电压幅度不足的情况时,上拉电阻和下拉电阻可以有效地对电平进行调整。例如,若前级电路只能输出 0V-3V 的电平,而后级系统需要 0V-5V 的高电平或低电平,上拉电阻可以强制拉高前级的输出电压,使其达到 3V-5V 之间的电平,从而满足后级系统对高电平的要求。同样地,当下级电路对低电平的要求更为严格时,下拉电阻能够将低电平进一步拉低,具体的拉低幅度取决于所选用的电阻阻值。

(二)具体作用

在 MOS 管开关电路中,通常会在 NMOS 管上加一个下拉电阻,而在 PMOS 管栅上加一个上拉电阻,阻值一般在 10KΩ 左右。

这些电阻在电路中主要起到以下三个关键作用:

这些电阻在电路中主要起到以下三个关键作用:

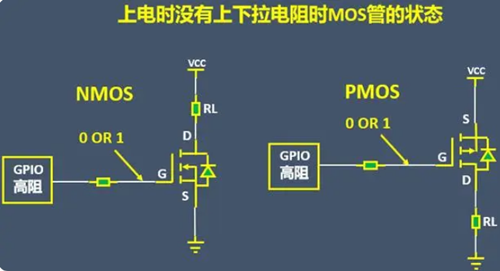

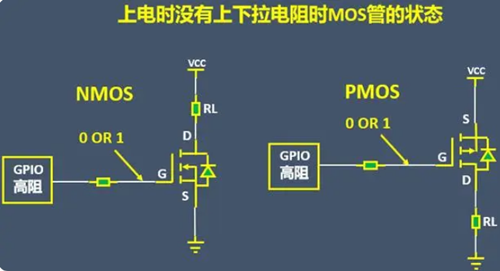

确定 MOS 管栅极电平 :MOS 管在上电瞬间会呈现高阻态,这种状态下栅极电平不确定,容易受到外界干扰。上拉电阻和下拉电阻可以确保 MOS 管栅极处于一个确定的电平状态,避免其因高阻态而受到干扰。对于 NMOS 管,下拉电阻使其栅极在无驱动信号时保持低电平,确保管子处于关闭状态;对于 PMOS 管,上拉电阻则使其栅极在无驱动信号时保持高电平,同样确保管子关闭。这样,MOS 管在上电时会一直保持关闭状态,直到单片机或其他控制单元发出控制信号来改变其状态。

防止静电击穿 :在 MOS 管栅极与源极之间存在寄生电容,当 MOS 管处于高阻态时,容易积累静电电荷。一旦静电电压超过 MOS 管的耐压值,就可能导致栅极击穿,损坏器件。上拉电阻和下拉电阻可以为这些积累的静电电荷提供一个泄放路径,使栅极电平保持稳定,防止静电击穿的发生。

提供放电路径 :MOS 管的栅极与源极之间的寄生电容在断电时需要进行放电。上拉电阻和下拉电阻能够为这些寄生电容提供放电路径,确保电路断电后 MOS 管能够快速、安全地释放储存的电荷,避免因电荷残留导致的电路异常或器件损坏。

三、总结

上拉电阻和下拉电阻在电路设计中起着至关重要的作用。上拉电阻的主要目的是确保 GPIO(低电平有效)在无信号输入时输入端的电平为高电平,防止因信号不确定而导致的电路误动作。相反地,下拉电阻则是为了保证 GPIO(高电平有效)在无信号输入时输入端的电平为低电平,同样是为了避免电路误动作,确保电路的稳定运行。

通过合理地使用上拉电阻和下拉电阻,可以有效地解决电路中因不确定电平信号引发的问题,提升电路的可靠性和稳定性,确保电子设备在各种工况下的正常运行。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280