LVDS:低电压差分信号电平标准解析

1. 概述

LVDS(Low Voltage Differential Signaling,低电压差分信号)是一种基于差分传输原理的低摆幅信号技术标准。其核心特征在于利用一对匹配的线路(差分线对)传输相位相反、幅度相等的信号,接收端通过检测两者间的电压差判别逻辑状态。该技术显著优势在于:

高速传输: 支持从155 Mbps至数千兆比特每秒(Gbps)的传输速率,典型应用范围可达2 Gbps以上。

低功耗: 采用恒定电流源驱动,静态功耗极低(典型值约1.2mW),且功耗基本不随频率升高而增加。

低噪声与高抗扰: 低压摆幅(典型值250-450mV)结合差分传输特性,有效抑制共模噪声干扰并大幅降低电磁辐射(EMI)。

低摆幅: 信号电压变化幅度小,有利于提升开关速度和降低功耗。

2. 标准定义

LVDS的核心电气规范由国际标准组织明确定义:

ANSI/TIA/EIA-644: 定义了LVDS的物理层电气接口标准。该标准推荐的最大数据传输速率为655 Mbps,同时指出其理论极限速率可达1.923 Gbps。

IEEE: 在多个相关标准(如LVDS物理层常用于高速接口标准如IEEE 1394b、Camera Link等)中引用和应用了LVDS技术。

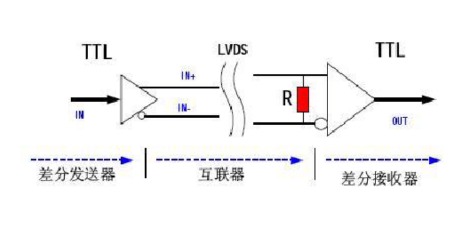

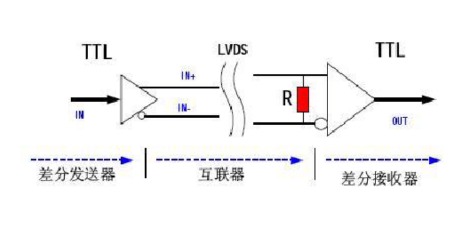

3. LVDS传输系统构成

一个完整的LVDS信号传输链路包含三个关键组件:

差分信号发送器 (Driver): 功能为将输入的单端信号(如TTL、CMOS电平)转换为满足LVDS电气规范的差分信号。通常由专用集成电路实现。

差分信号传输介质 (Interconnect): 由承载差分信号的物理通道构成,常见形式包括PCB差分走线对或平衡屏蔽电缆。在传输链路的终端,需配置匹配电阻(标准值为100Ω,实际应用中可在100Ω至120Ω范围内选择)以消除信号反射,保证信号完整性。

差分信号接收器 (Receiver): 功能为检测差分线上的电压差,并将其还原为标准的单端逻辑电平信号(如TTL、CMOS)。同样由专用集成电路实现。

4. LVDS电平电气特性详解

LVDS接口的电气特性是其优越性能的基础:

偏置电压: 通常采用约1.2V的共模电压作为基准。

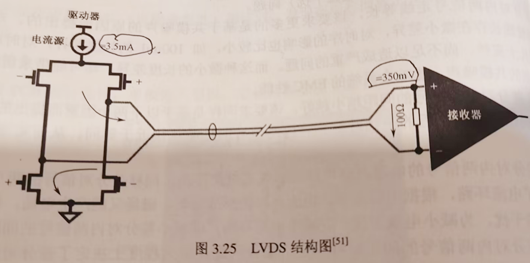

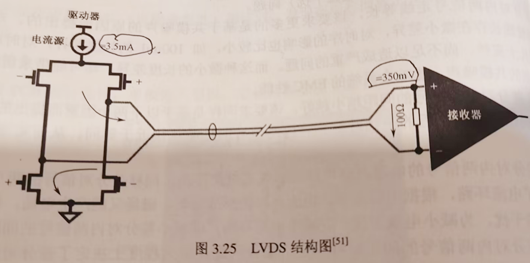

信号摆幅: 差分信号的峰峰值电压摆幅(VOD)在250mV至450mV之间。产生原理如下:

驱动器采用恒流源(典型值3.5mA)驱动差分线对。

接收器呈现高输入阻抗。

驱动电流主要流经终端匹配电阻(RTerm)。

差分电压计算:VOD = I_Output * RTerm

典型值:3.5mA * 100Ω = 350mV

上限值:3.5mA * 120Ω ≈ 420mV

逻辑判定: 接收器通过判别差分电压的极性来识别逻辑状态:

驱动器输出电流正向流经匹配电阻(如从Driver+流入,Driver-流出)产生正差分电压,对应于逻辑“1”。

驱动器输出电流反向流经匹配电阻产生负差分电压,对应于逻辑“0”。

功耗特性:

典型功耗可计算为 P = I_Output * VOD (典型值:3.5mA * 350mV ≈ 1.2mW)。

由于采用恒流源驱动,功耗基本保持恒定,不受传输频率变化的显著影响。

5. 核心优势总结

卓越的高速性能: 支持数百Mbps至数Gbps的高速数据传输,广泛应用于高速串行接口(如PCIe, SATA辅助信道)、视频接口(如FPD-Link)、背板通信等领域。

极致功耗效率: 在同等速率的高速逻辑电平中,LVDS具有显著的功耗优势。

优异的信号完整性: 差分传输机制提供强大的共模噪声抑制(CMR)能力,低摆幅特性有效降低EMI。

设计适用性广: 特别适用于点对点或点对多点的板级高速互连应用场景(例如SPI4.2等并行总线物理层接口)。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280