CMOS反相器功耗分析

一、CMOS反相器基础结构与工作原理

CMOS 反相器由 NMOS 晶体管与 PMOS 晶体管组合而成。当输入端接入逻辑高电压时,PMOS 晶体管截止,NMOS 晶体管导通,输出端子经低电阻路径连接至 0V。而当输入端为逻辑低电压时,PMOS 导通,NMOS 截止,输出端经低电阻路径连接到 VDD。由此实现逻辑高电平输入对应逻辑低电平输出,逻辑低电平输入对应逻辑高电平输出的反转功能。

二、动态功耗详解

尽管 CMOS 反相器在稳态下近乎不消耗电流,但在逻辑转换过程中会产生成功率损耗,动态功耗主要包含开关功耗与短路功耗两方面。

(一)开关功耗

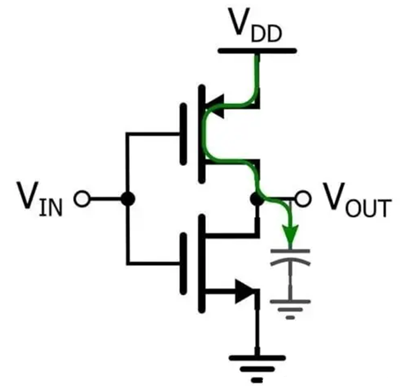

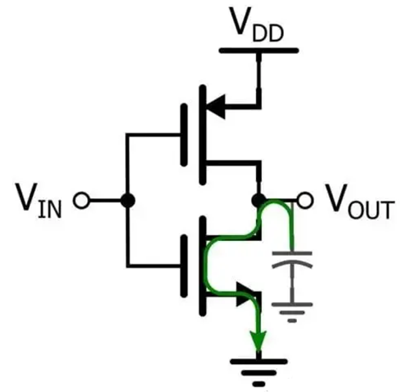

输入逻辑转换时,瞬态电流流动用于给电路中的电容充电或放电。低输出转高输出时,电流流通以对负载电容充电,使输出电压上升至 VDD 水准,如下图充电电流路径所示。

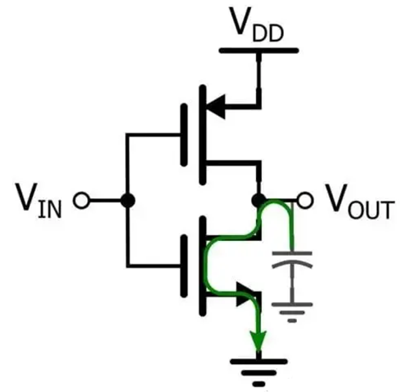

高输出转低输出时,电容则通过相应路径放电,致使输出电压降低。

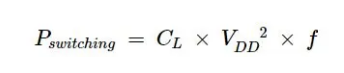

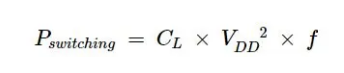

估算 CMOS 反相器开关损耗可依据公式 P = CL × VDD² × f,其中 CL 为负载电容,VDD 为电源电压,f 为开关频率。CL × VDD² 计算单个开关周期所需能量,乘以每秒循环次数 f 后转换为功率形式。

高输出转低输出时,电容则通过相应路径放电,致使输出电压降低。

估算 CMOS 反相器开关损耗可依据公式 P = CL × VDD² × f,其中 CL 为负载电容,VDD 为电源电压,f 为开关频率。CL × VDD² 计算单个开关周期所需能量,乘以每秒循环次数 f 后转换为功率形式。

(二)短路功耗

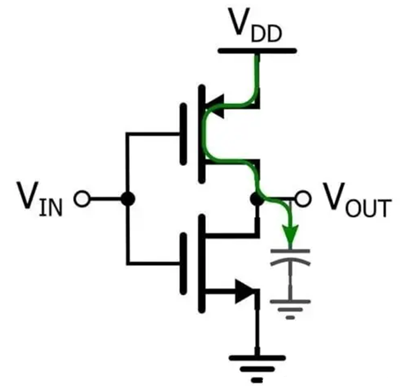

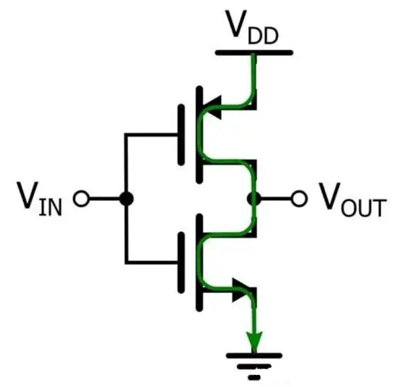

短路功耗源于逻辑电平转换期间的瞬态短路电流。CMOS 反相器处于稳定逻辑状态时,仅有一个晶体管导通,电流难以从 VDD 流向地。但在逻辑状态转换的短暂交叉期内,NMOS 和 PMOS 晶体管均呈现一定程度的导电性,形成短路路径,电流经此短路从 VDD 流向地,造成能量损失,如下图所示逻辑电平转换时的短路情形。

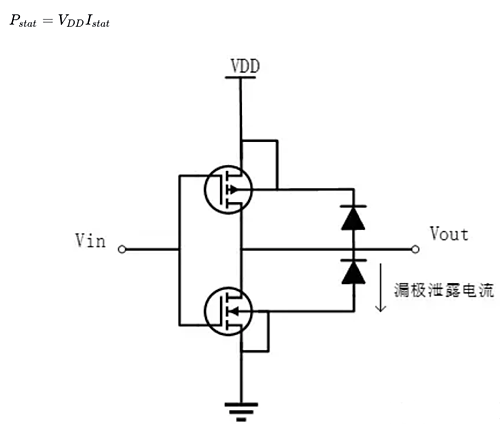

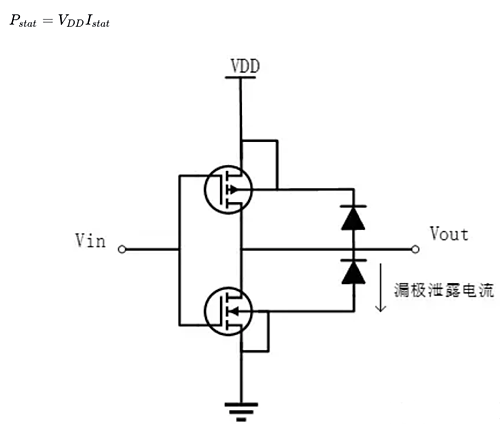

三、静态功耗探究

理想状况下,CMOS 反相器稳态工作时 PMOS 与 NMOS 不同时导通,电源与地之间无直流通路,静态功耗归零。然而实际电路中,源或漏与衬底间的反偏二极管存在微弱泄漏电流 Istat,此泄漏电流引发的静态功耗可表示为 P = VDD × Istat 。

泄漏电流产生的根源在于源或漏与衬底之间存在反偏二极管,在一定电压下会有少量载流子跨越结区,形成微小电流。这些反偏二极管的特性、晶体管的几何结构、半导体材料的特性以及工作温度等多因素均会对泄漏电流的大小产生影响。温度升高时,半导体材料中载流子的热激发增强,泄漏电流往往会增大,从而增加静态功耗。此外,晶体管的制造工艺 imperfections 也可能导致泄漏电流超出理想水平。

泄漏电流产生的根源在于源或漏与衬底之间存在反偏二极管,在一定电压下会有少量载流子跨越结区,形成微小电流。这些反偏二极管的特性、晶体管的几何结构、半导体材料的特性以及工作温度等多因素均会对泄漏电流的大小产生影响。温度升高时,半导体材料中载流子的热激发增强,泄漏电流往往会增大,从而增加静态功耗。此外,晶体管的制造工艺 imperfections 也可能导致泄漏电流超出理想水平。

深入理解 CMOS 反相器的功耗特性,对于优化电路设计、降低能耗以及提升整体性能具有极为关键的意义。在实际应用中,需综合考量动态与静态功耗,采取有效的优化策略,以实现 CMOS 反相器在不同工作场景下的最佳性能表现。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280