CMOS反相器电路解析

一、电路原理图与物理版图

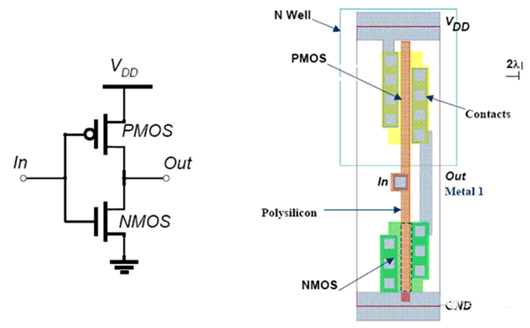

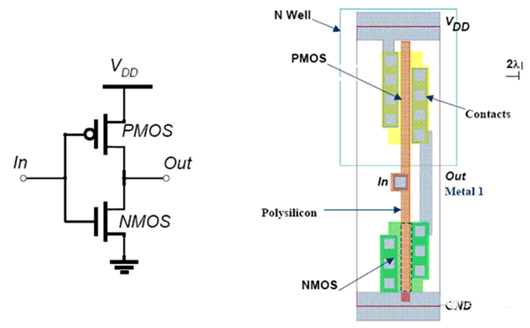

CMOS反相器由NMOS和PMOS晶体管组成,其电路原理图和物理版图如下图所示。物理版图相当于MASK图形,集成电路制造基于此图形,经光刻、生长、注入等工艺逐层实现。因此,任何电路图最终需转换为物理版图供生产。

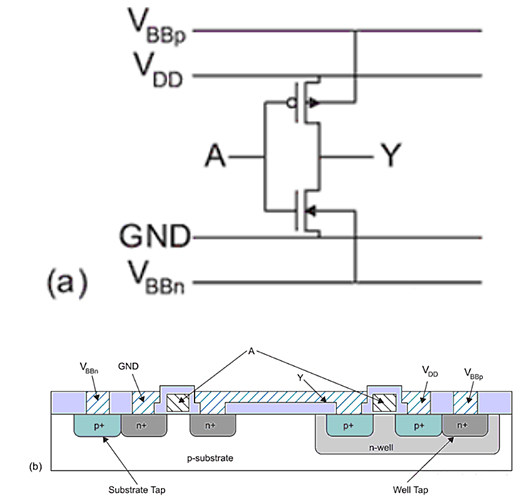

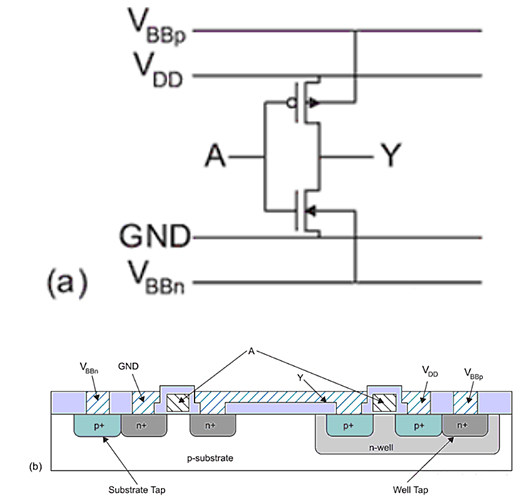

CMOS反相器实际剖面图如下,展示了其层叠结构。

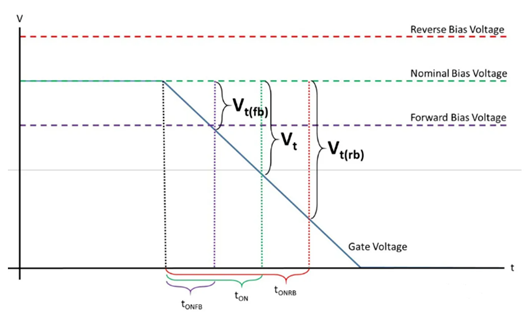

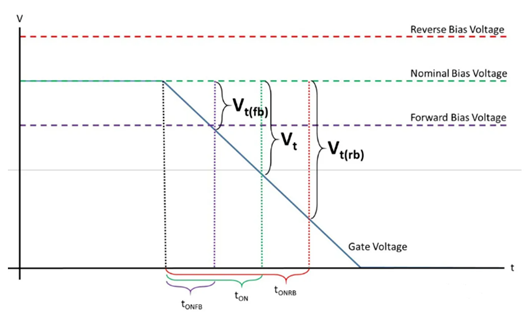

通常,VDD与VBBp连接且接至VDD,作为PMOS的源端;VBBn与GND连接并接地,充当NMOS的源端。随着工艺尺寸缩小,为节省面积,VBBp和VBBn不再与每一门电路的VDD和GND连接,而是每隔几个电路连接一次。不过,这会导致衬底偏置电压(VBS)与源端出现minor电压差,进而改变阈值电压VT。VBS与VT呈反比关系:VBS越大,VT越小;VBS越小,VT越大。

对于数字集成电路工程师而言,了解衬底偏置电压对VT的影响即可。在先进工艺中,为实现低功耗设计,BodyBiasingGenerator(BBG)可微调偏置电压,在功耗与性能间做出权衡。降低VT能提升性能,但会增加漏电;提高VT可减少漏电,但对性能有负面影响。

二、电路分析

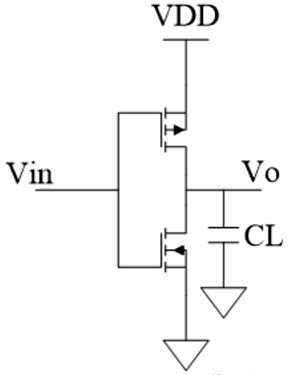

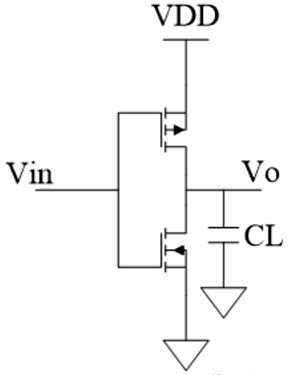

(一)电路组成与负载电容

CMOS反相器电路包含一个负载电容CL。对于CMOS门电路,其输出需驱动负载。一般而言,CMOS门电路的负载是金属连线与地之间的电容以及下一级电路输入栅极与地之间的电容。由于MOSFET是电压控制电流器件,仅靠电流无法实现逻辑传递。负载电容在充电和放电过程中,使其节点在VDD和地电势间跳变,从而传递逻辑数值。

(二)反相器转移特性曲线

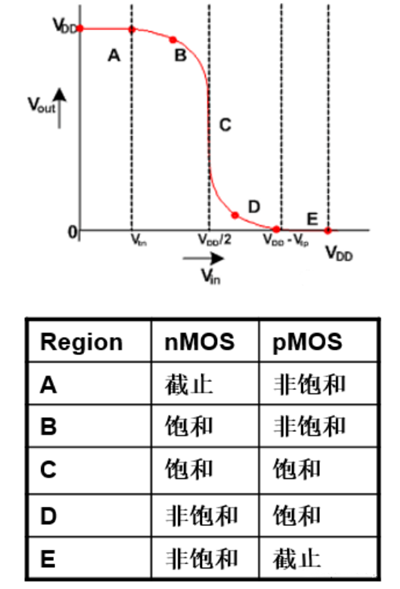

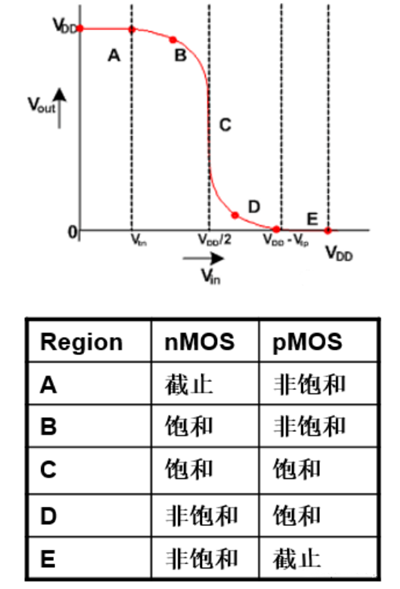

假设PMOS和NMOS的VT值相同,输入电压变化引起的输出电压变化曲线(反相器转移特性曲线)如下:

A区域:当输入电压Vin在0V到VTN之间时,NMOS截止,PMOS处于非饱和状态,但无电流通路,因此无电流流过,输出电压保持不变。

B区域:Vin在VTN到1/2VDD之间时,NMOS处于饱和状态,PMOS处于非饱和状态。由于PMOS的VDS不大,电流较小,电容放电速度较慢。

C区域:当Vin在1/2VDD附近时,NMOS和PMOS同时处于饱和状态,放电速度突然增大。此时,PMOS很快达到饱和状态(VDS增加),而NMOS很快达到非饱和状态(VDS减少),随后进入D区域。

D区域:Vin在1/2VDD到接近(VDD-VTP)的区间时,NMOS处于非饱和状态,PMOS处于饱和状态。由于NMOS的VDS不大,电流较小,电容放电速度较慢。

E区域:当Vin大于VDD-VTP时,PMOS截止,无电流通路,输出电压固定在0V。

从上述特性可见,输入电压为VDD时,输出电压为0V;输入电压为0V时,输出电压为VDD,满足反相器的逻辑关系。

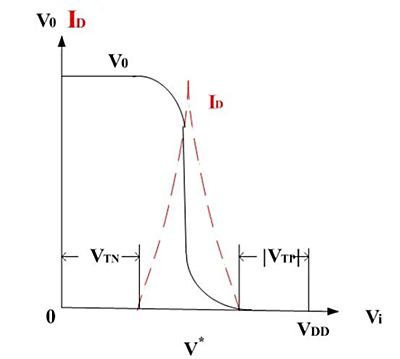

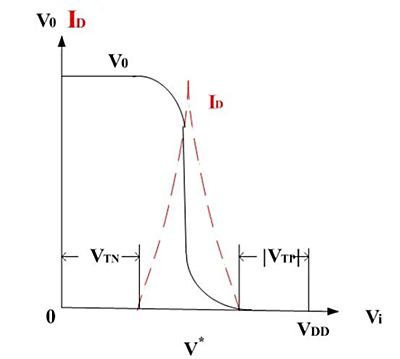

(三)输入电压与电路电流的关系

分析表明,当输入电压小于NMOS的VT或大于VDD-|VTP|时,电路几乎不产生电流。仅在中间区间,才会产生较大电流,尤其当两个管子均处于饱和状态时。这种特性意味着电路在不发生状态翻转时几乎不消耗电流,而一旦发生翻转,借助NMOS和PMOS的互补性,可迅速实现状态转换,进而提升电路性能。

通过以上分析,深入理解CMOS反相器的电路原理和特性,有助于在数字集成电路设计中更好地运用和优化反相器,以实现高性能、低功耗的电路设计。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280