一、CMOS闩锁效应及其影响

CMOS闩锁效应(Latch-up)是CMOS晶片中的一种潜在故障。由于寄生的NPN和PNP三极管相互导通,会在电源VDD和地VSS之间形成低阻抗通路,导致大电流通过芯片,有造成永久性损坏的风险。这种效应通常由静电放电(ESD)、瞬态电源干扰等特定电压或电流条件触发,会导致电路在电源与地之间形成短路,使电路承受远大于正常工作电流的冲击,可能迅速烧毁电路。

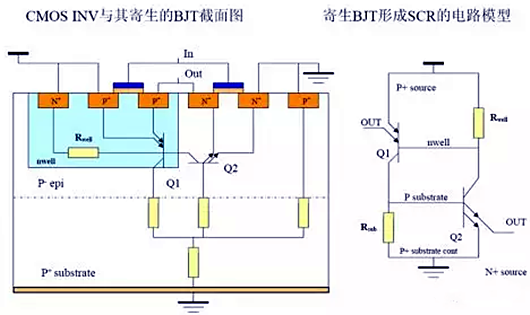

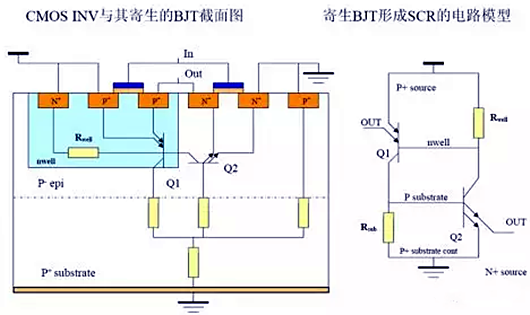

二、CMOS闩锁效应原理

CMOS工艺中形成的寄生双极晶体管结构是闩锁效应的核心原因。在PMOS中,源和漏的重掺杂p+型有源区、N阱(N-Well)扩散区和P型衬底(P-sub)会形成纵向寄生的PNP结构;在NMOS中,则形成横向寄生的NPN结构。正常情况下,这些寄生晶体管处于截止状态,不会影响电路。然而,当外部条件(如电压过冲、静电放电等)导致其中一个寄生晶体管的集电极电流突然增大到一定值时,该晶体管导通,并通过正反馈机制触发另一个寄生晶体管导通,从而在VDD和VSS之间形成低阻抗通路,引发大电流。

三、CMOS闩锁效应的产生原因

电压过冲:当输出端(Vout)的电位过冲超过VDD一定值(如0.7V)时,PNP寄生晶体管会导通,进而触发正反馈机制,导致闩锁效应的发生。

静电放电(ESD):静电放电现象会在瞬间产生高压,可能使输出端电位远高于VDD,导致NPN和PNP寄生晶体管同时导通,形成闩锁。

电源干扰:瞬态电源干扰也可能导致器件管脚的电压超过电源电压或低于地,从而触发闩锁效应。

电感感应回冲:快速变化的电流在电感上会产生感应电动势,这种感应电动势可能通过电路耦合到器件管脚,导致电压过冲或下冲,进而触发闩锁。

四、CMOS闩锁效应解决措施

(一)工艺制造角度

采用浅槽隔离技术(STI)、SOI工艺技术、倒掺杂阱技术和外延技术等手段来减小寄生电阻和电容,降低闩锁效应的风险。这些技术能够优化晶片的内部结构,减少寄生参数的影响,提高晶片的抗闩锁能力。

(二)版图设计角度

使用Guardring(保护环)来隔离敏感区域,减少寄生效应的影响。保护环是一种在版图设计中用于隔离不同电路区域的结构,通过在敏感区域周围设置保护环,可以有效阻挡寄生效应的传播,保护电路的正常工作。

确保电源线和地线足够强壮,并打满Contact孔以降低电阻。这样可以减少电源线和地线上的电压降,提高电路的供电稳定性,降低因电源线和地线电阻引起的闩锁风险。

注意将NMOS和PMOS拉开一定距离以降低触发闩锁的可能性。合理布局NMOS和PMOS的位置,增加它们之间的间距,可以减小寄生晶体管之间的相互影响,降低闩锁效应发生的概率。

(三)电路设计角度

在电路电源或地变动较大的电路附近增加相关耦合电容以稳定电压。耦合电容可以在一定程度上吸收电路中的瞬态电压变化,稳定电源和地的电压,减少电压波动对电路的影响,从而降低闩锁效应的发生风险。

在PAD附近增加保护二极管以防止静电放电对电路的影响。保护二极管可以在静电放电发生时,为静电电流提供一个低阻抗的放电路径,避免静电电压冲击电路,保护电路免受静电损坏。

在电路的主通路上串联大电阻以限制电流的大小。大电阻可以限制电路中的最大电流,防止过大的电流通过芯片,降低因大电流引起的闩锁效应风险,同时也有助于保护其他电路元件免受过流损坏。

〈烜芯微/XXW〉专业制造二极管,三极管,MOS管,桥堆等,20年,工厂直销省20%,上万家电路电器生产企业选用,专业的工程师帮您稳定好每一批产品,如果您有遇到什么需要帮助解决的,可以直接联系下方的联系号码或加QQ/微信,由我们的销售经理给您精准的报价以及产品介绍

联系号码:18923864027(同微信)

QQ:709211280